Question: 4. Suppose we have a 5-stage pipeline processor: Fetch Decode Execute -> Memory Write Back Also suppose we have the following program 1 2 3

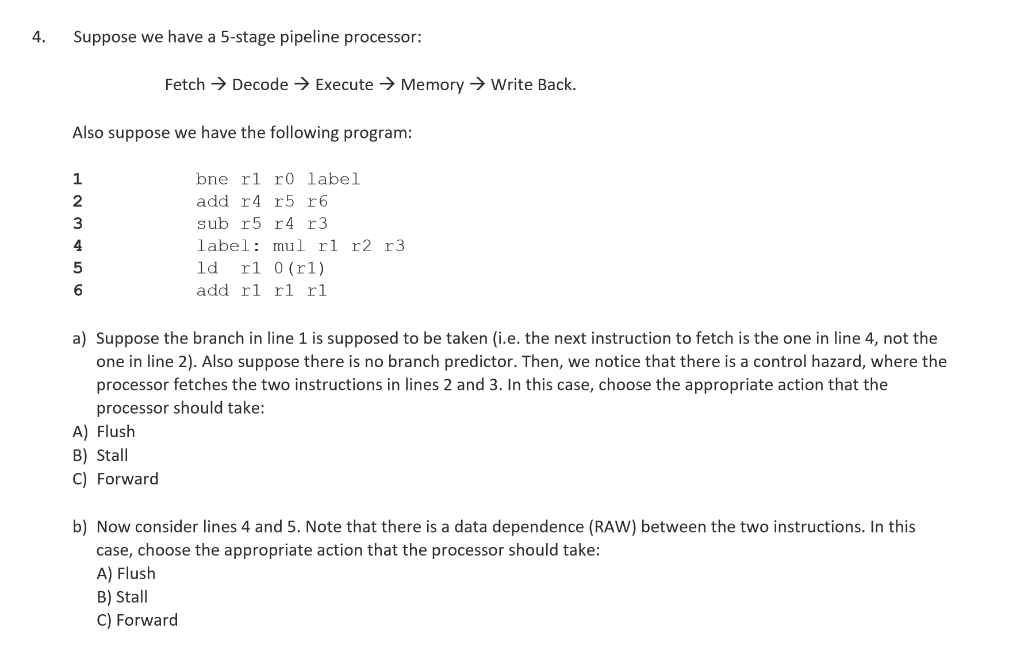

4. Suppose we have a 5-stage pipeline processor: Fetch Decode Execute -> Memory Write Back Also suppose we have the following program 1 2 3 4 5 6 bne rl r0 label add r4 r5 r6 sub r5 r4 r 3 label: mul rl r2 r3 ld rl 0 (r1) add r1 rl rl a) Suppose the branch in line 1 is supposed to be taken (i.e. the next instruction to fetch is the one in line 4, not the one in line 2). Also suppose there is no branch predictor. Then, we notice that there is a control hazard, where the processor fetches the two instructions in lines 2 and 3. In this case, choose the appropriate action that the processor should take: A) Flush B) Stall C) Forward b) Now consider lines 4 and 5. Note that there is a data dependence (RAW) between the two instructions. In this case, choose the appropriate action that the processor should take A) Flush B) Stall C) Forward 4. Suppose we have a 5-stage pipeline processor: Fetch Decode Execute -> Memory Write Back Also suppose we have the following program 1 2 3 4 5 6 bne rl r0 label add r4 r5 r6 sub r5 r4 r 3 label: mul rl r2 r3 ld rl 0 (r1) add r1 rl rl a) Suppose the branch in line 1 is supposed to be taken (i.e. the next instruction to fetch is the one in line 4, not the one in line 2). Also suppose there is no branch predictor. Then, we notice that there is a control hazard, where the processor fetches the two instructions in lines 2 and 3. In this case, choose the appropriate action that the processor should take: A) Flush B) Stall C) Forward b) Now consider lines 4 and 5. Note that there is a data dependence (RAW) between the two instructions. In this case, choose the appropriate action that the processor should take A) Flush B) Stall C) Forward

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts