Question: 4.7Suppose a 32-bit instruction takes the following format: OPCODE SR DRIMM If there are 60 opcodes and 32 registers, what is the range of values

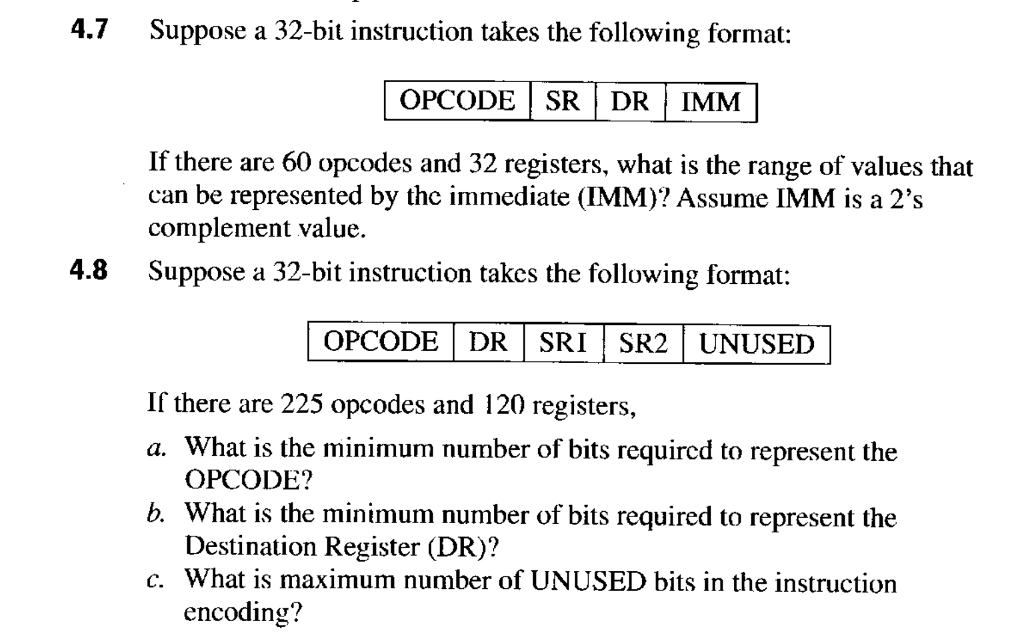

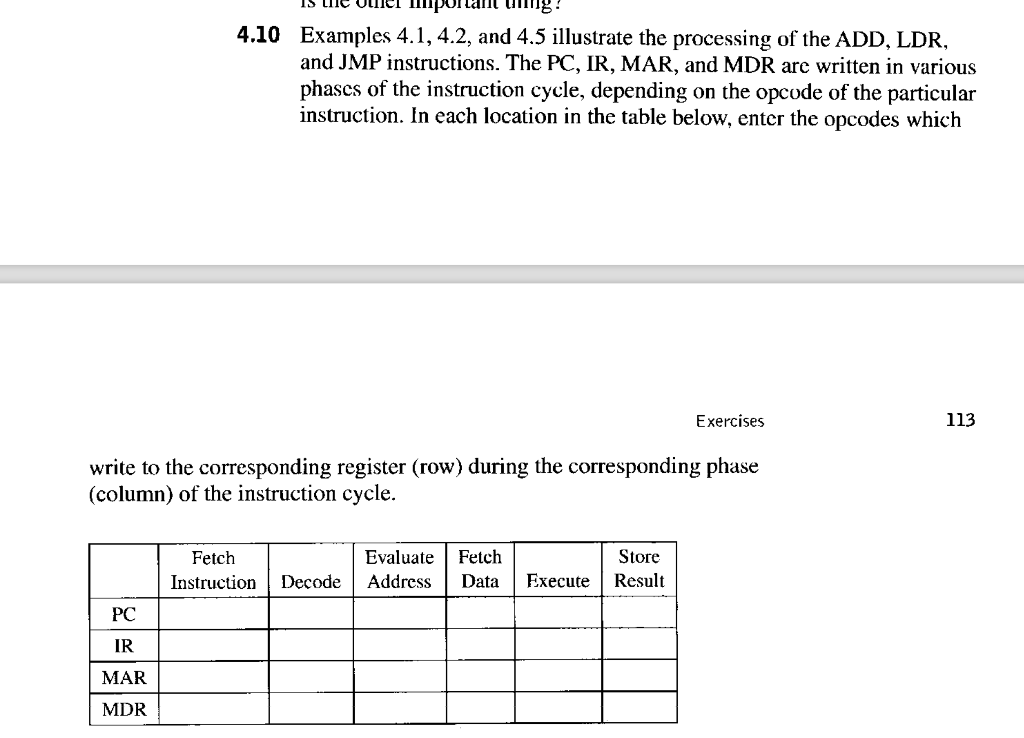

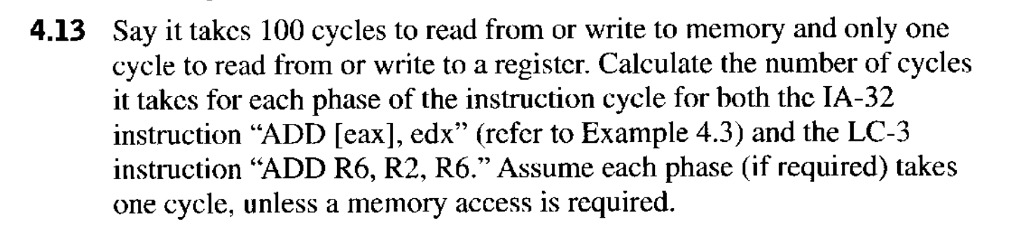

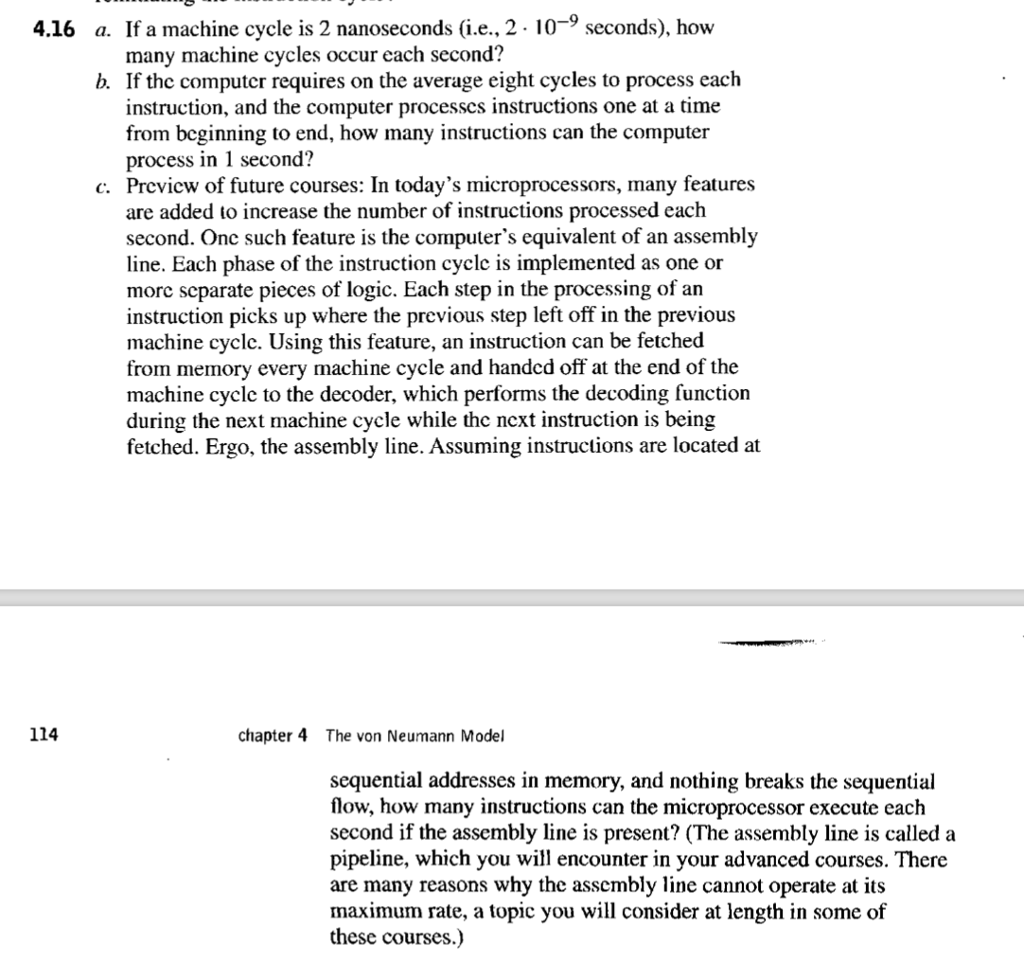

4.7Suppose a 32-bit instruction takes the following format: OPCODE SR DRIMM If there are 60 opcodes and 32 registers, what is the range of values that can be represented by thc immediate (IMM)? Assume IMM is a 2's complement value. 4.8 Suppose a 32-bit instruction takes the following format: OPCODE DR SRI SR2 UNUSED If there are 225 opcodes and 120 registers, a. What is the minimum number of bits required to represent the OPCODE? Destination Register (DR)? encoding? b. What is the minimum number of bits required to represent the c. What is maximum number of UNUSED bits in the instruction 4.7Suppose a 32-bit instruction takes the following format: OPCODE SR DRIMM If there are 60 opcodes and 32 registers, what is the range of values that can be represented by thc immediate (IMM)? Assume IMM is a 2's complement value. 4.8 Suppose a 32-bit instruction takes the following format: OPCODE DR SRI SR2 UNUSED If there are 225 opcodes and 120 registers, a. What is the minimum number of bits required to represent the OPCODE? Destination Register (DR)? encoding? b. What is the minimum number of bits required to represent the c. What is maximum number of UNUSED bits in the instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts