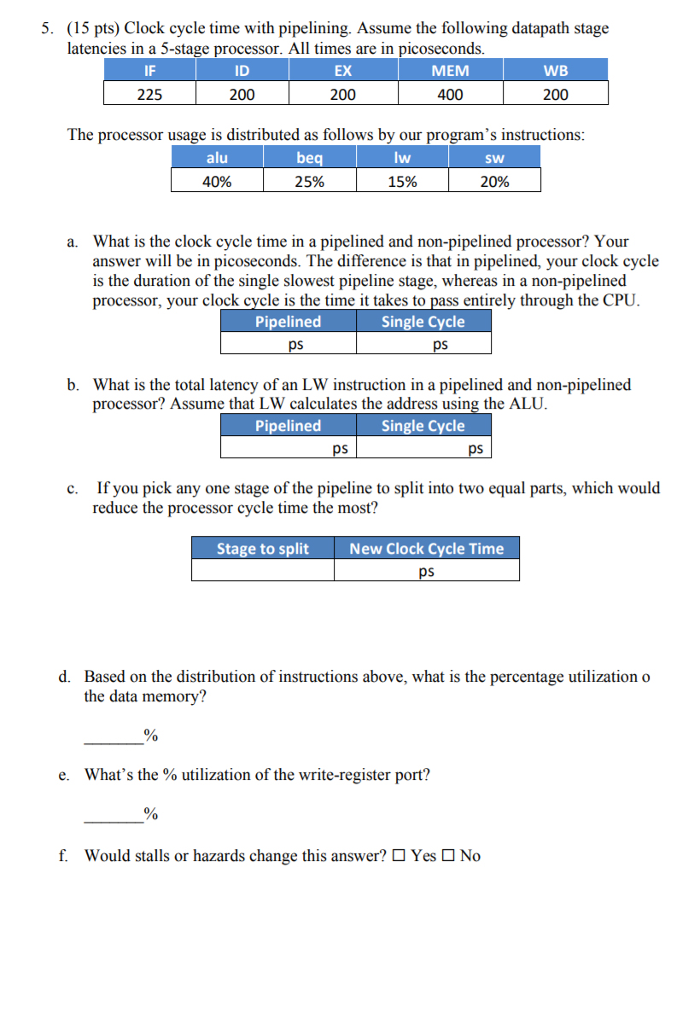

Question: 5. (15 pts) Clock cycle time with pipelining. Assume the following datapath stage latencies in a 5-stage processor. All times are in picoseconds MEM 400

5. (15 pts) Clock cycle time with pipelining. Assume the following datapath stage latencies in a 5-stage processor. All times are in picoseconds MEM 400 IF ID EX WB 225 200 200 200 The processor usage is distributed as follows by our program's instructions: alu beq SW 40% 25% 15% 20% What is the clock cycle time in a pipelined and non-pipelined processor? Your answer will be in picoseconds. The difference is that in pipelined, your clock cycle is the duration of the single slowest pipeline stage, whereas in a non-pipelined processor, your clock cycle is the time it takes to pass entirely through the CPU a. Pipelined Single Cycle b. What is the total latency of an LW instruction in a pipelined and non-pipelined processor? Assume that LW calculates the address using the ALU Pipelined Single Cycle If you pick any one stage of the pipeline to split into two equal parts, which would reduce the processor cycle time the most? c. Stage to split New Clock Cycle Time d. Based on the distribution of instructions above, what is the percentage utilization o the data memory? e. What's the % utilization of the write-register port? Would stalls or hazards change this answer? Yes No 5. (15 pts) Clock cycle time with pipelining. Assume the following datapath stage latencies in a 5-stage processor. All times are in picoseconds MEM 400 IF ID EX WB 225 200 200 200 The processor usage is distributed as follows by our program's instructions: alu beq SW 40% 25% 15% 20% What is the clock cycle time in a pipelined and non-pipelined processor? Your answer will be in picoseconds. The difference is that in pipelined, your clock cycle is the duration of the single slowest pipeline stage, whereas in a non-pipelined processor, your clock cycle is the time it takes to pass entirely through the CPU a. Pipelined Single Cycle b. What is the total latency of an LW instruction in a pipelined and non-pipelined processor? Assume that LW calculates the address using the ALU Pipelined Single Cycle If you pick any one stage of the pipeline to split into two equal parts, which would reduce the processor cycle time the most? c. Stage to split New Clock Cycle Time d. Based on the distribution of instructions above, what is the percentage utilization o the data memory? e. What's the % utilization of the write-register port? Would stalls or hazards change this answer? Yes No

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts