Question: 5. An instruction execution path will take T ns to execute an instruction in one-stage pipeline. However, this logic path can be divided into any

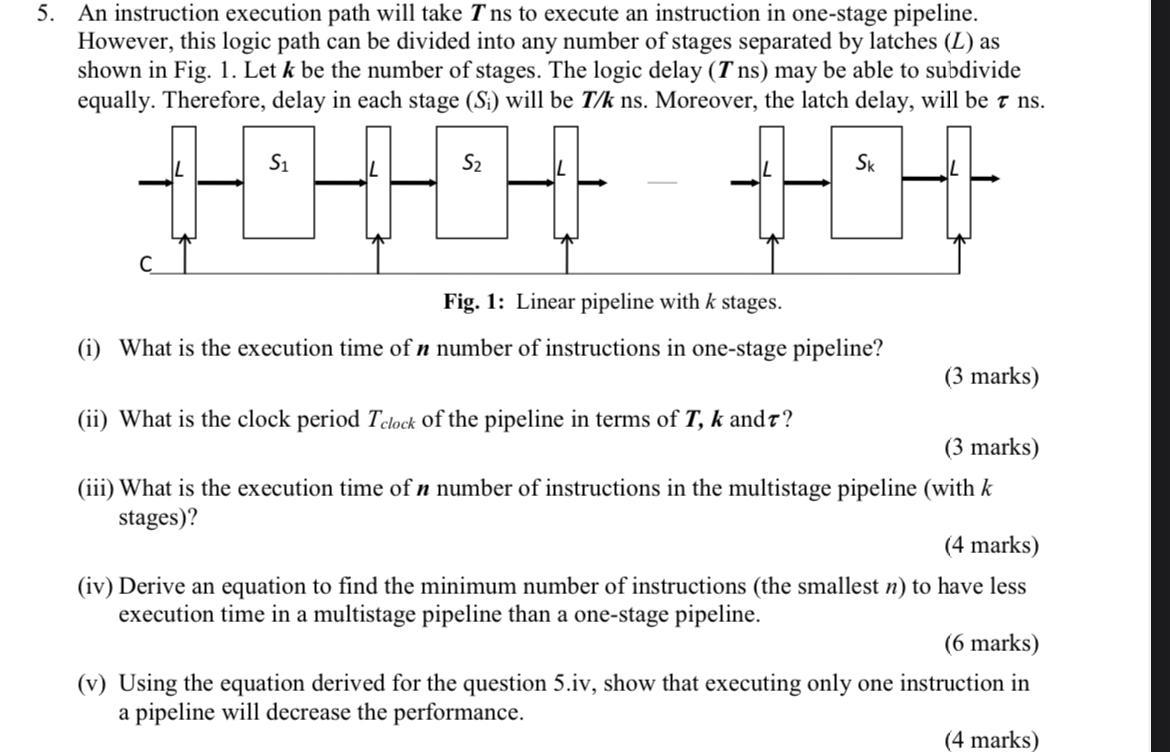

5. An instruction execution path will take T ns to execute an instruction in one-stage pipeline. However, this logic path can be divided into any number of stages separated by latches (L) as shown in Fig. 1. Let k be the number of stages. The logic delay (T ns) may be able to subdivide equally. Therefore, delay in each stage (Si) will be T/k ns. Moreover, the latch delay, will be t ns. Si S2 Sk HH HH Fig. 1: Linear pipeline with k stages. (i) What is the execution time of n number of instructions in one-stage pipeline? (3 marks) (ii) What is the clock period Tclock of the pipeline in terms of T, k andt? (3 marks) (iii) What is the execution time of n number of instructions in the multistage pipeline (with k stages)? (4 marks) (iv) Derive an equation to find the minimum number of instructions (the smallest n) to have less execution time in a multistage pipeline than a one-stage pipeline. (6 marks) (v) Using the equation derived for the question 5.iv, show that executing only one instruction in a pipeline will decrease the performance. (4 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts