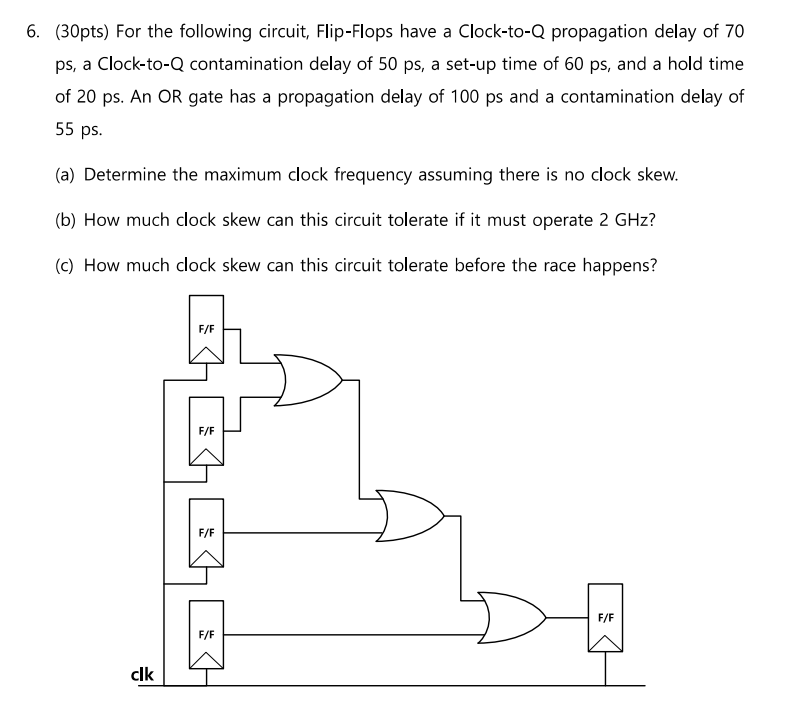

Question: 6 . ( 3 0 pts ) For the following circuit, Flip - Flops have a Clock - to - Q propagation delay of 7

pts For the following circuit, FlipFlops have a ClocktoQ propagation delay of ps a ClocktoQ contamination delay of ps a setup time of ps and a hold time of ps An OR gate has a propagation delay of ps and a contamination delay of ps

a Determine the maximum clock frequency assuming there is no clock skew.

b How much clock skew can this circuit tolerate if it must operate GHz

c How much clock skew can this circuit tolerate before the race happens?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock