Question: 9 18 M . W M F D E2 E3 3 Pipeline (Reverse Engineering) The following piece of code runs on a pipelined microprocessor as

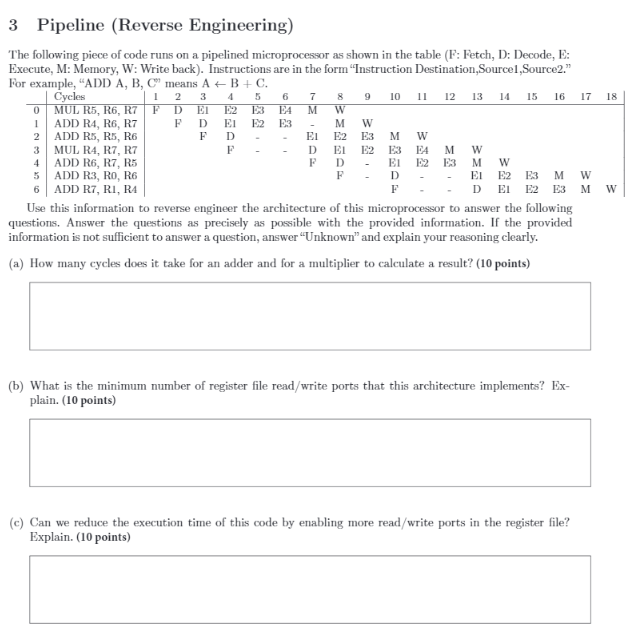

9 18 M . W M F D E2 E3 3 Pipeline (Reverse Engineering) The following piece of code runs on a pipelined microprocessor as shown in the table (F: Fetch, D: Decode, E: Execute, M: Memory, W: Write back). Instructions are in the form "Instruction Destination,Sourcel,Source2." For example, "ADD A, B, C means A+B+C. Cycles 1 2 10 11 12 13 14 15 16 17 MUL R5, R6, R7 TDI 1:2 EA ADD R4, R6, R7 w ADD R5, RS, R6 F D E2 E3 M w MUL R4, R7, R7 M 4 ADD R6, R7, R5 FD E3 5 ADD R3, RO, R6 El E2 E3 Mw 6 ADD R7, RI, R4 E2 E3 Use this information to reverse engineer the architecture of this microprocessor to answer the following questions. Answer the questions as precisely as possible with the provided information. If the provided information is not sufficient to answer a question, answer Unknown" and explain your reasoning clearly. (a) How many cycles does it take for an adder and for a multiplier to calculate a result? (10 points) 0 1 2 3 EI F D E2 E4 w M w E3 EI D F F D M W (b) What is the minimum number of register file read/write ports that this architecture implements? Ex- plain. (10 points) (c) Can we reduce the execution time of this code by enabling more read/write ports in the register file? Explain. (10 points) (d) Does this architecture implement any data forwarding? If so, how is data forwarding done between pipeline stages? Explain. (10 points) 8/10 (e) Is it possible to run this code faster by adding more data forwarding paths? If it is, how? Explain. (10 points)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts