Question: a ) Design a completely labeled 4 - bit serial - in / parallel out shift register using negative edge triggered D flip - flop

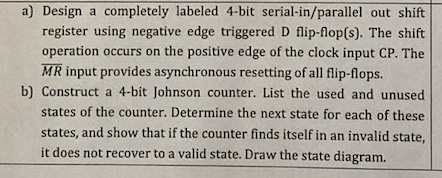

a Design a completely labeled bit serialinparallel out shift register using negative edge triggered D flipflops The shift operation occurs on the positive edge of the clock input CP The overlineM R input provides asynchronous resetting of all flipflops.

b Construct a bit Johnson counter. List the used and unused states of the counter. Determine the next state for each of these states, and show that if the counter finds itself in an invalid state, it does not recover to a valid state. Draw the state diagram.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock