Question: A Finite State Machine has the following delay values for it's state FFs and NextState Decoder: 1. State Flip-Flops propagation delay (from Clock edge to

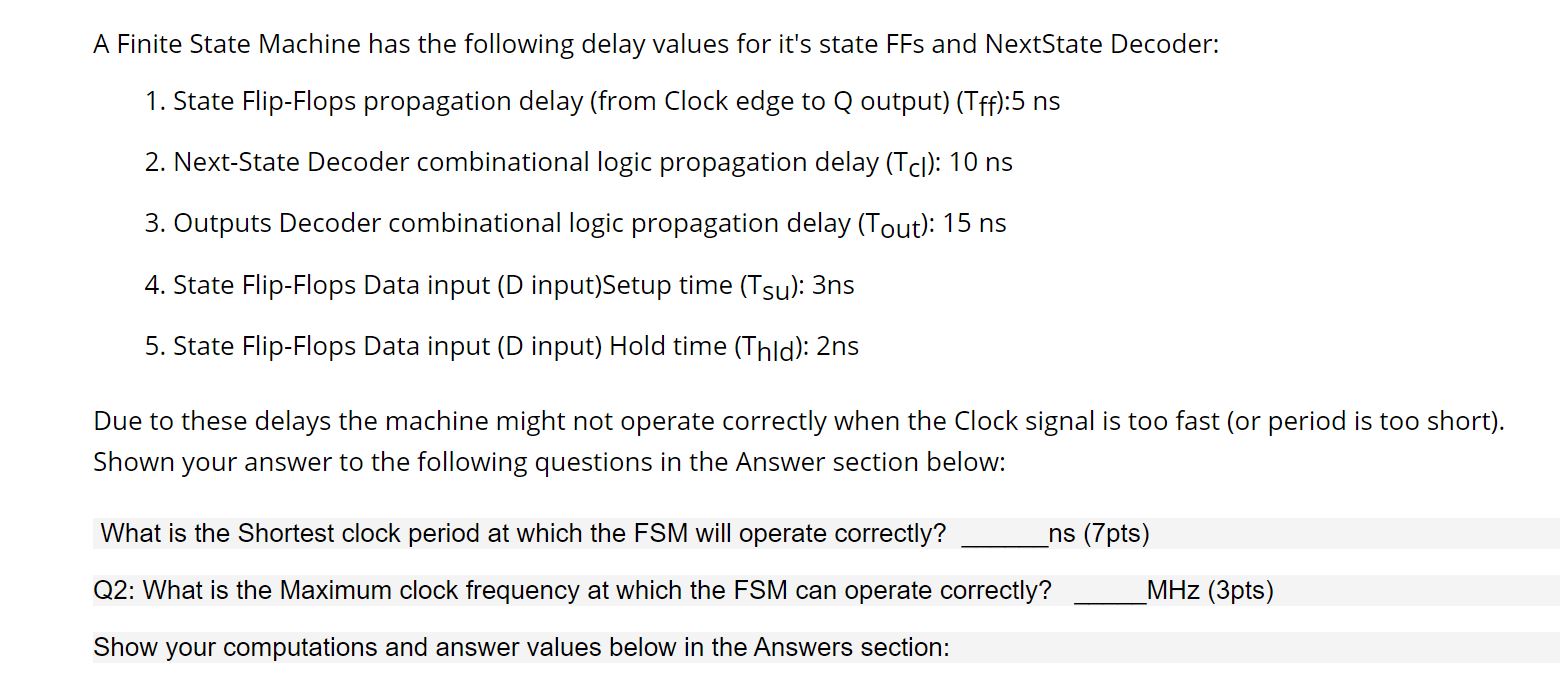

A Finite State Machine has the following delay values for it's state FFs and NextState Decoder: 1. State Flip-Flops propagation delay (from Clock edge to Q output) (Tff):5 ns 2. Next-State Decoder combinational logic propagation delay (TCI): 10 ns 3. Outputs Decoder combinational logic propagation delay (Tout): 15 ns 4. State Flip-Flops Data input (D input)Setup time (Tsu): 3ns 5. State Flip-Flops Data input (D input) Hold time (Thld): 2ns Due to these delays the machine might not operate correctly when the Clock signal is too fast (or period is too short). Shown your answer to the following questions in the Answer section below: What is the Shortest clock period at which the FSM will operate correctly? ns (7pts) Q2: What is the Maximum clock frequency at which the FSM can operate correctly? MHz (3pts) Show your computations and answer values below in the Answers

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts