Question: a ) Indicate in which cycle the add instruction from the next iteration appears in the pipeline assuming branches are resolved in the MEM stage.

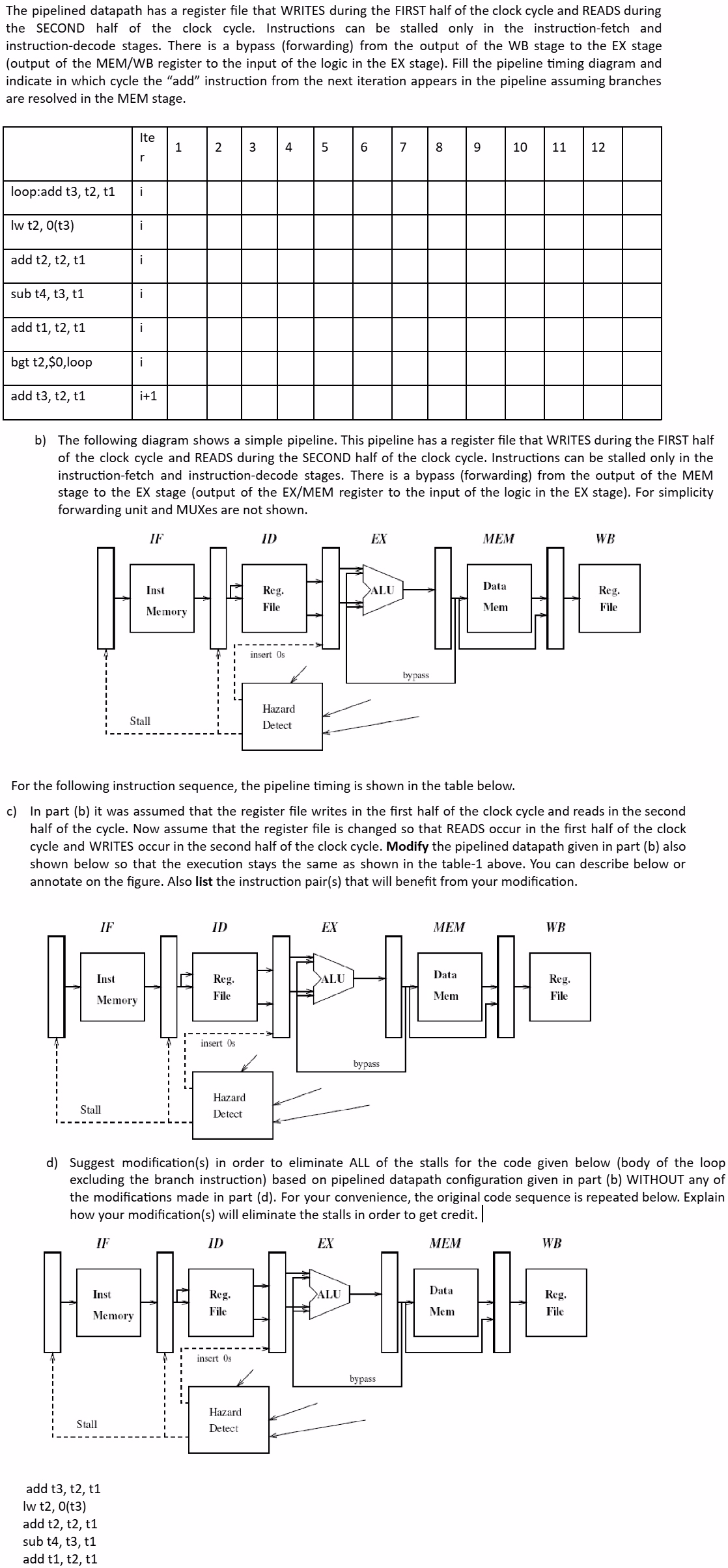

a Indicate in which cycle the "add" instruction from the next iteration appears in the pipeline assuming branches are resolved in the MEM stage.

b The following diagram shows a simple pipeline. This pipeline has a register file that WRITES during the FIRST half of the clock cycle and READS during the SECOND half of the clock cycle. Instructions can be stalled only in the instructionfetch and instructiondecode stages. There is a bypass forwarding from the output of the MEM stage to the EX stage output of the EXMEM register to the input of the logic in the EX stage For simplicity forwarding unit and MUXes are not shown.

For the following instruction sequence, the pipeline timing is shown in the table below.

c In part b it was assumed that the register file writes in the first half of the clock cycle and reads in the second half of the cycle. Now assume that the register file is changed so that READS occur in the first half of the clock cycle and WRITES occur in the second half of the clock cycle. Modify the pipelined datapath given in part b also shown below so that the execution stays the same as shown in the table above. You can describe below or annotate on the figure. Also list the instruction pairs that will benefit from your modification.

d Suggest modifications in order to eliminate ALL of the stalls for the code given below body of the loop excluding the branch instruction based on pipelined datapath configuration given in part b WITHOUT any of the modifications made in part d For your convenience, the original code sequence is repeated below. Explain how your modifications will eliminate the stalls in order to get credit.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock