Question: A pipelined architecture that can process floating-point (FP) instructions was explained in a lecture. Show a pipeline timing chart for the instruction sequence below when

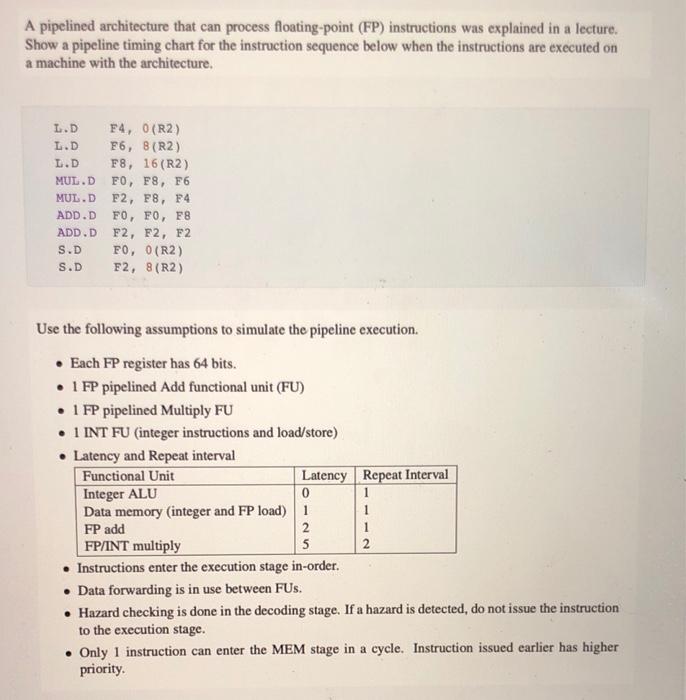

A pipelined architecture that can process floating-point (FP) instructions was explained in a lecture. Show a pipeline timing chart for the instruction sequence below when the instructions are executed on a machine with the architecture, L.D F4, 0(R2) L.D F6, 8(R2) 1.D F8, 16 (R2) MUL.D FO, F8, F6 MUL.DF2, F8, F4 ADD.D FO, FO, F8 ADD.D F2, F2, F2 S.D FO, 0(R2) S.D F2, 8(R2) Use the following assumptions to simulate the pipeline execution. Each FP register has 64 bits. 1 FP pipelined Add functional unit (FU) 1 FP pipelined Multiply FU . 1 INT FU (integer instructions and load/store) Latency and Repeat interval Functional Unit Latency Repeat Interval Integer ALU 0 1 Data memory (integer and FP load) 1 1 FP add 2 1 FP/INT multiply 5 2 Instructions enter the execution stage in-order. . Data forwarding is in use between FUS. Hazard checking is done in the decoding stage. If a hazard is detected, do not issue the instruction to the execution stage. Only 1 instruction can enter the MEM stage in a cycle. Instruction issued earlier has higher priority. A pipelined architecture that can process floating-point (FP) instructions was explained in a lecture. Show a pipeline timing chart for the instruction sequence below when the instructions are executed on a machine with the architecture, L.D F4, 0(R2) L.D F6, 8(R2) 1.D F8, 16 (R2) MUL.D FO, F8, F6 MUL.DF2, F8, F4 ADD.D FO, FO, F8 ADD.D F2, F2, F2 S.D FO, 0(R2) S.D F2, 8(R2) Use the following assumptions to simulate the pipeline execution. Each FP register has 64 bits. 1 FP pipelined Add functional unit (FU) 1 FP pipelined Multiply FU . 1 INT FU (integer instructions and load/store) Latency and Repeat interval Functional Unit Latency Repeat Interval Integer ALU 0 1 Data memory (integer and FP load) 1 1 FP add 2 1 FP/INT multiply 5 2 Instructions enter the execution stage in-order. . Data forwarding is in use between FUS. Hazard checking is done in the decoding stage. If a hazard is detected, do not issue the instruction to the execution stage. Only 1 instruction can enter the MEM stage in a cycle. Instruction issued earlier has higher priority

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts