Question: A processor has 16-bit addresses, 256 byte pages, and an 8-entry fully associative TLB with LRU replacement (the LRU field is 3 bits and encodes

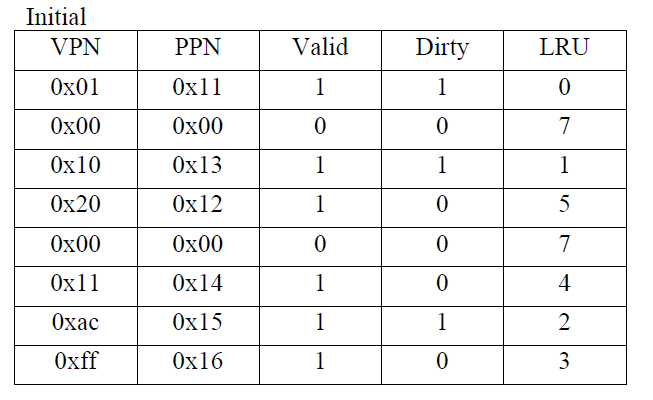

A processor has 16-bit addresses, 256 byte pages, and an 8-entry fully associative TLB with LRU replacement (the LRU field is 3 bits and encodes the order in which pages were accessed, 0 being the most recent). At some time instant, the TLB for the current process is the initial state given in the table below. Assume that all current page table entries are in the initial TLB.

Assume also that all pages can be read from and written to. Fill in the final state of the TLB according to the access pattern below.

Free physical pages: 0x17, 0x18, 0x19

Access pattern:

Read 0x11f0

Write 0x1301

Write 0x20ae

Write 0x2332

Read 0x20ff

Write 0x3415

Initial VPN 0x01 0x00 0x10 0x20 0x00 0x11 0xac 0xff PPN 0x11 0x00 0x13 0x12 0x00 0x14 0x15 0x16 Valid Dirty LRU

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts