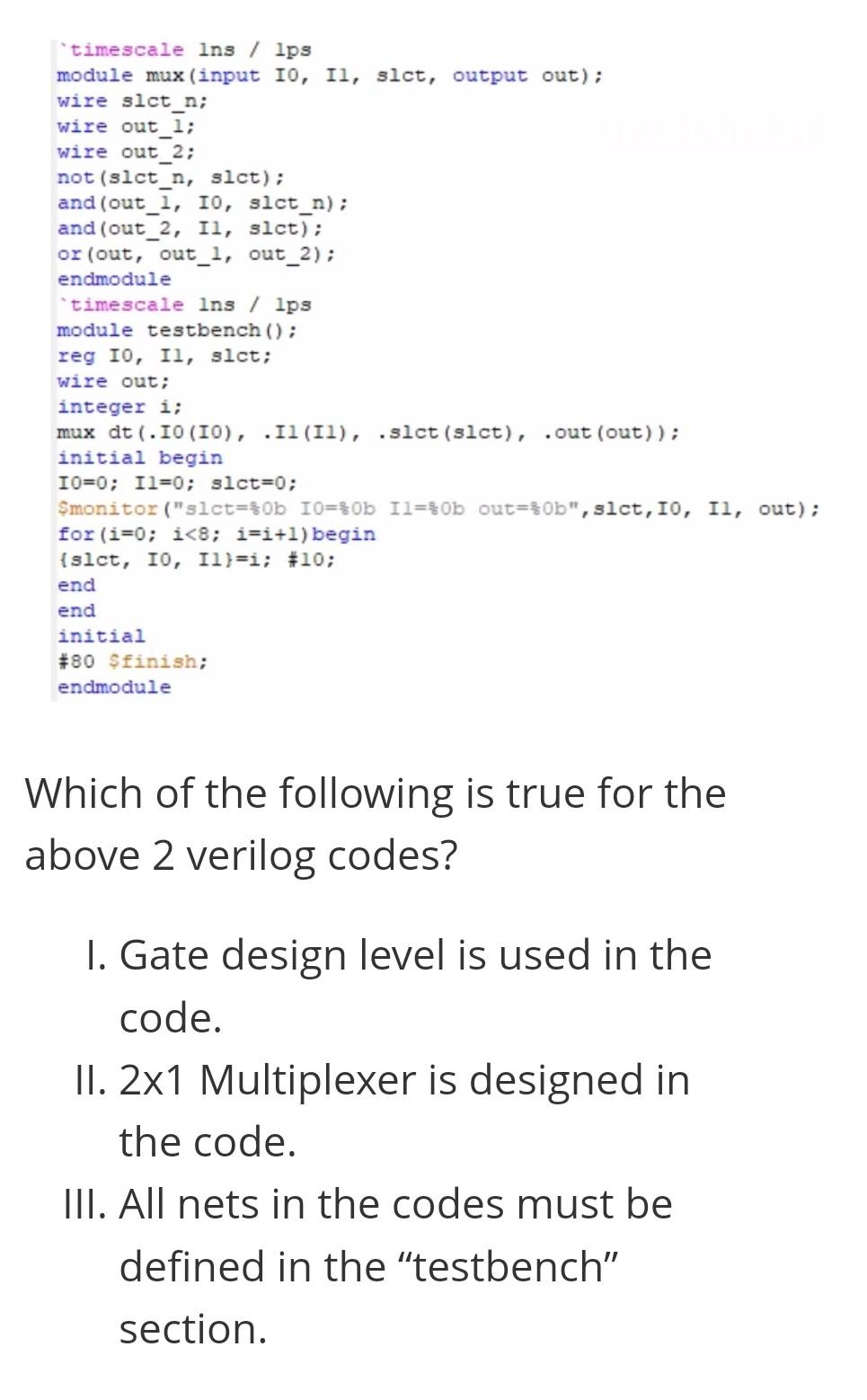

Question: Answer Only Please timescale Ins/ lps module mux (input 10, Il, slct, output out); wire slct_n; wire out_1; wire out_2; not (slct_n, slct); and (out_1,

Answer Only Please

"timescale Ins/ lps module mux (input 10, Il, slct, output out); wire slct_n; wire out_1; wire out_2; not (slct_n, slct); and (out_1, 10, slct_n); and (out_2, Il, slct); or (out, out_1, out_2); endmodule "timescale Ins/ lps module testbench(); reg 10, 11, slct; wire out; integer i; mux dt (.IO (10), Il(11), .slct (slct), .out (out)); initial begin IO=0; Il=0; slct=0; $monitor ("sct=sob 10=0b Il=sob out=30b",slct, 10, 11, out); for (i=0; i

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts