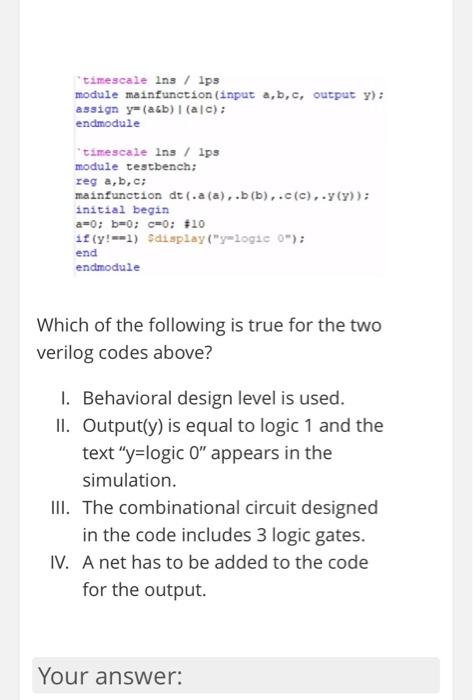

Question: timescale ins / Ips module mainfunction (input a, b, c, output y): assign y=(ab) (alc): endmodule timescale ins / Ips module testbench; reg a,b,c; mainfunction

"timescale ins / Ips module mainfunction (input a, b, c, output y): assign y=(ab) (alc): endmodule "timescale ins / Ips module testbench; reg a,b,c; mainfunction dt(.a(a)..b(b), (c),y()); initial begin a=0; b=0; c=0: 110 1f (y!--1) sdisplay("y-logic 0); end endmodule Which of the following is true for the two verilog codes above? 1. Behavioral design level is used. II. Output(y) is equal to logic 1 and the text "y=logic 0" appears in the simulation. III. The combinational circuit designed in the code includes 3 logic gates. IV. A net has to be added to the code for the output. Your

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts