Question: Architicture Class - Cache Coherence A bus based multiprocessor system has 2 processors and a memory connected by a bus. It uses the MSI cache

Architicture Class - Cache Coherence

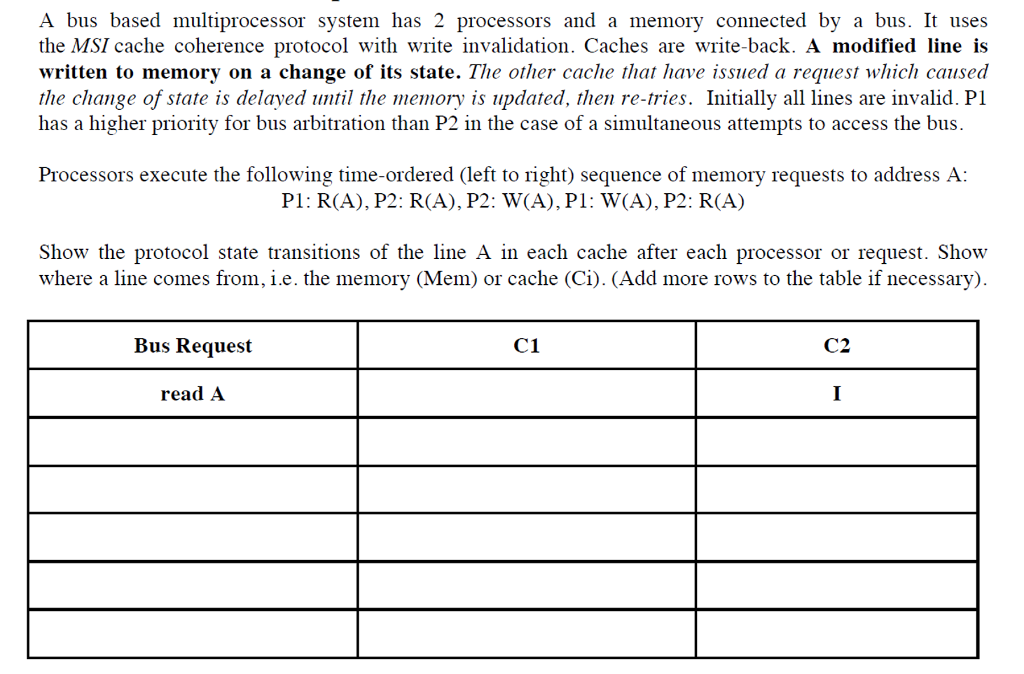

A bus based multiprocessor system has 2 processors and a memory connected by a bus. It uses the MSI cache coherence protocol with write invalidation. Caches are write-back. A modified line is written to memory on a change of its state. The other cache that have issued a request which caused the change of state is delayed until the memory is updated, then re-tries. Initially all lines are invalid. P1 has a higher priority for bus arbitration than P2 in the case of a simultaneous attempts to access the bus. Processors execute the following time-ordered (left to right) sequence of memory requests to address A: P1: R(A), P2: R(A), P2: W(A), P1: W(A), P2 R(A) Show the protocol state transitions of the line A in each cache after each processor or request. Show where a line comes from, i.e. the memory (Mem) or cache (Ci). (Add more rows to the table if necessary)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts