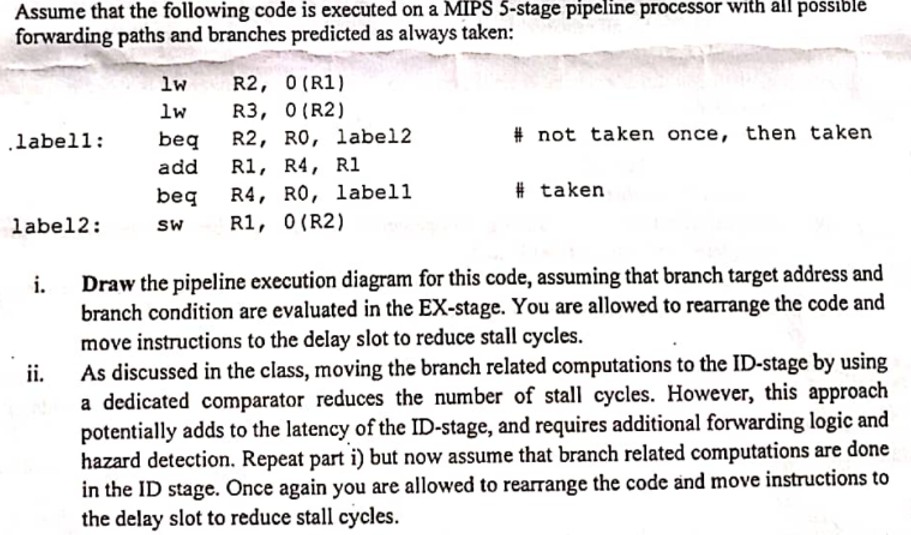

Question: Assume that the following code is executed on a MIPS 5 - stage pipeline processor with all possible forwarding paths and branches predicted as always

Assume that the following code is executed on a MIPS stage pipeline processor with all possible

forwarding paths and branches predicted as always taken:

i Draw the pipeline execution diagram for this code, assuming that branch target address and

branch condition are evaluated in the EXstage. You are allowed to rearrange the code and

move instructions to the delay slot to reduce stall cycles.

ii As discussed in the class, moving the branch related computations to the IDstage by using

a dedicated comparator reduces the number of stall cycles. However, this approach

potentially adds to the latency of the IDstage, and requires additional forwarding logic and

hazard detection. Repeat part i but now assume that branch related computations are done

in the ID stage. Once again you are allowed to rearrange the code and move instructions to

the delay slot to reduce stall cycles.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock