Question: Cache Simulator: Make a few changes in the C code on the Github link to meet these requirements for the L1 cache simulator ( 2-way

Cache Simulator: Make a few changes in the C code on the Github link to meet these requirements for the L1 cache simulator ( 2-way set associate cache of size 32 bytes.)

Github link: https://github. com/vinceix/Cache-Simulator

Again, this is C code. All you have to do is make a few changes to meet those requirements from the code that was given to you.

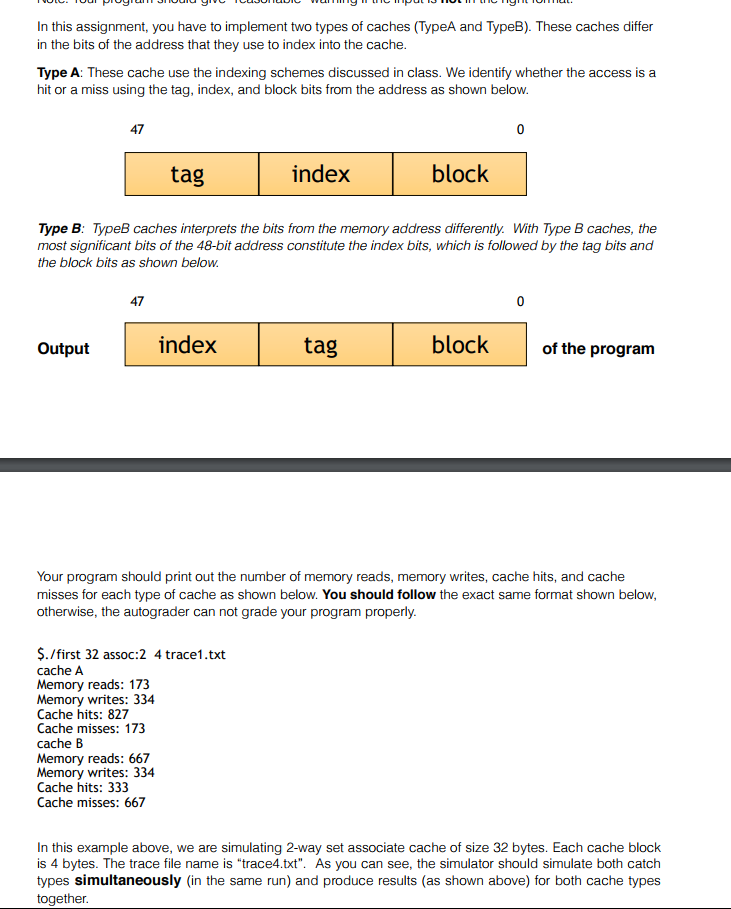

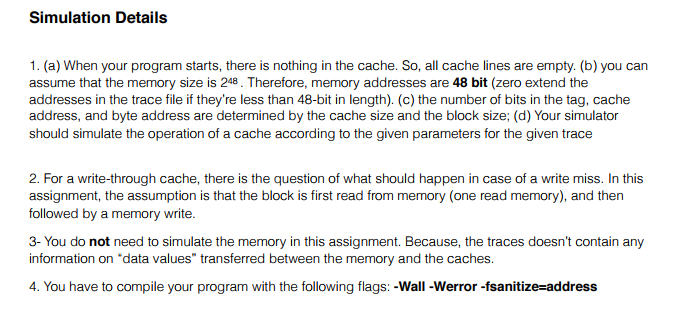

In this assignment, you have to implement two types of caches (TypeA and TypeB). These caches differ in the bits of the address that they use to index into the cache Type A: These cache use the indexing schemes discussed in class. We identify whether the access is a hit or a miss using the tag, index, and block bits from the address as shown below. index block tag Type B. TypeB caches interprets the bits from the memory address differently. With Type B caches, the most significant bits of the 48-bit address constitute the index bits, which is followed by the tag bits and the block bits as shown below. 47 index block of the program tag output Your program should print out the number of memory reads, memory writes, cache hits, and cache misses for each type of cache as shown below. You should follow the exact same format shown below, otherwise, the autograder can not grade your program properly $./first 32 assoc: 4 trace1.txt cache A Memory reads: 173 Memory writes: 334 Cache hits: 827 Cache misses: 173 cache B Memory reads: 667 Memory writes: 334 Cache hits: 333 Cache misses: 667 In this example above, we are simulating 2-way set associate cache of size 32 bytes. Each cache block is 4 bytes. The trace file name is "trace4.txt". As you can see, the simulator should simulate both catch types simultaneously (in the same run) and produce results (as shown above) for both cache types together In this assignment, you have to implement two types of caches (TypeA and TypeB). These caches differ in the bits of the address that they use to index into the cache Type A: These cache use the indexing schemes discussed in class. We identify whether the access is a hit or a miss using the tag, index, and block bits from the address as shown below. index block tag Type B. TypeB caches interprets the bits from the memory address differently. With Type B caches, the most significant bits of the 48-bit address constitute the index bits, which is followed by the tag bits and the block bits as shown below. 47 index block of the program tag output Your program should print out the number of memory reads, memory writes, cache hits, and cache misses for each type of cache as shown below. You should follow the exact same format shown below, otherwise, the autograder can not grade your program properly $./first 32 assoc: 4 trace1.txt cache A Memory reads: 173 Memory writes: 334 Cache hits: 827 Cache misses: 173 cache B Memory reads: 667 Memory writes: 334 Cache hits: 333 Cache misses: 667 In this example above, we are simulating 2-way set associate cache of size 32 bytes. Each cache block is 4 bytes. The trace file name is "trace4.txt". As you can see, the simulator should simulate both catch types simultaneously (in the same run) and produce results (as shown above) for both cache types together

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts