Question: Can someone help me write a test bench in VHDL that tests all cases for the following VHDL code (which is a 4bit adder): library

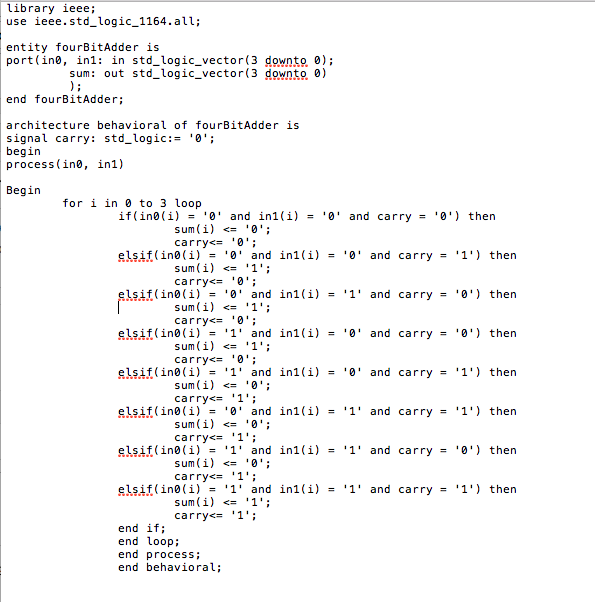

Can someone help me write a test bench in VHDL that tests all cases for the following VHDL code (which is a 4bit adder):

library ieee: use ieee. std-logic-1164 all; entity fourBitAdder is port (ino, in 1: in std_logic_vector (3 downto 0 sum out std_logic_vector (3 downto 0 end fourB itAdder architecture behavioral of fourBitAdder is signal carr std logic '0'; begin process n0 in1) (i Begin for i in 0 to 3 loop if (in (i) '0' and in (i) '0' and carry '0') then sum (i) carry '0' elsif (ine (i) '0' and in (i) '0' and carry '1') then sum (i) '1'; carry '0'; elsif (ino (i) 'e' and in 1 (i) '1' and carry '0') then sum (i) 1'; carry '0' elsif sum (i) '1' and in (i) '0' and carry '0') then (ino (i) '1'; carry '0' elsif (ino (i) '1' and in (i) '0' and carry '1') then sum (i) .0 carry '1'; elsif (ine (i) '0' and in 1 (i) '1' and carry '1') then sum (i) elsif carry '1'; carry then (ine (i) '1' and in 1 (i) '1' and '0') sum (i) '0' carry '1'; elsif (ino (i) '1' and in (i) '1' and carry '1') then sum (i) 1'; carry '1'; end if end loop; end process; end behavioral library ieee: use ieee. std-logic-1164 all; entity fourBitAdder is port (ino, in 1: in std_logic_vector (3 downto 0 sum out std_logic_vector (3 downto 0 end fourB itAdder architecture behavioral of fourBitAdder is signal carr std logic '0'; begin process n0 in1) (i Begin for i in 0 to 3 loop if (in (i) '0' and in (i) '0' and carry '0') then sum (i) carry '0' elsif (ine (i) '0' and in (i) '0' and carry '1') then sum (i) '1'; carry '0'; elsif (ino (i) 'e' and in 1 (i) '1' and carry '0') then sum (i) 1'; carry '0' elsif sum (i) '1' and in (i) '0' and carry '0') then (ino (i) '1'; carry '0' elsif (ino (i) '1' and in (i) '0' and carry '1') then sum (i) .0 carry '1'; elsif (ine (i) '0' and in 1 (i) '1' and carry '1') then sum (i) elsif carry '1'; carry then (ine (i) '1' and in 1 (i) '1' and '0') sum (i) '0' carry '1'; elsif (ino (i) '1' and in (i) '1' and carry '1') then sum (i) 1'; carry '1'; end if end loop; end process; end behavioral

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts