Question: Can soemone help with this VHDL program please? You should try to use only the synthesizable features of VHDL. In particular, only one wait statement

Can soemone help with this VHDL program please? You should try to use only the synthesizable features of VHDL. In particular, only one "wait" statement is allowed in a process. The "wait for" statements are not allowed in your implementation, but might be used in your test benches.

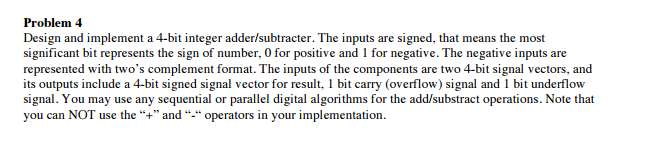

Problem 4 Design and implement a 4-bit integer adder/subtracter. The inputs are signed, that means the most significant bit represents the sign of number, 0 for positive and l for negative. The negative inputs are represented with two's complement format. The inputs of the components are two 4-bit signal vectors, and its outputs include a 4-bit signed signal vector for result, 1 bit carry (overflow) signal and l bit underflow signal. You may use any sequential or parallel digital algorithms for the add/substract operations. Note that you can NOT use the and operators in your implementation

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts