Question: Complete the following combinational circuit design problems and upload your scanned solutions. Each is worth five (5) points. 1. Given the following circuit specification,

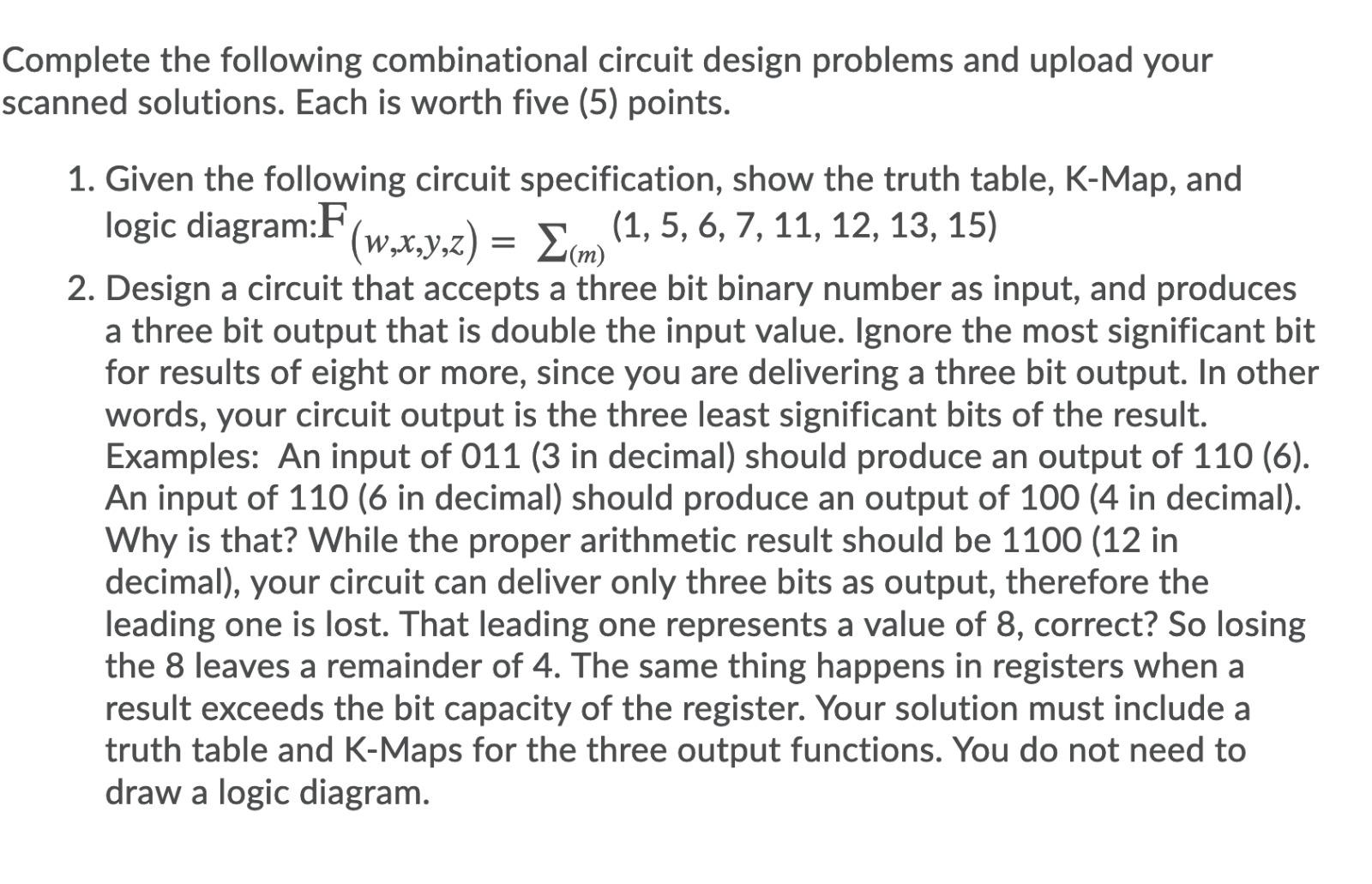

Complete the following combinational circuit design problems and upload your scanned solutions. Each is worth five (5) points. 1. Given the following circuit specification, show the truth table, K-Map, and logic diagram:F(w,x,y,z) (m) (1, 5, 6, 7, 11, 12, 13, 15) 2. Design a circuit that accepts a three bit binary number as input, and produces a three bit output that is double the input value. Ignore the most significant bit for results of eight or more, since you are delivering a three bit output. In other words, your circuit output is the three least significant bits of the result. Examples: An input of 011 (3 in decimal) should produce an output of 110 (6). An input of 110 (6 in decimal) should produce an output of 100 (4 in decimal). Why is that? While the proper arithmetic result should be 1100 (12 in decimal), your circuit can deliver only three bits as output, therefore the leading one is lost. That leading one represents a value of 8, correct? So losing the 8 leaves a remainder of 4. The same thing happens in registers when a result exceeds the bit capacity of the register. Your solution must include a truth table and K-Maps for the three output functions. You do not need to draw a logic diagram. =

Step by Step Solution

There are 3 Steps involved in it

Question 1 In the given expression we have four inputs w x y z Fill 1 for the terms 15671... View full answer

Get step-by-step solutions from verified subject matter experts