Question: computer archiceture (b) A hypothetical computer system has a hierarchical memory architecture consists of cache memory of size 32 KB with a block size of

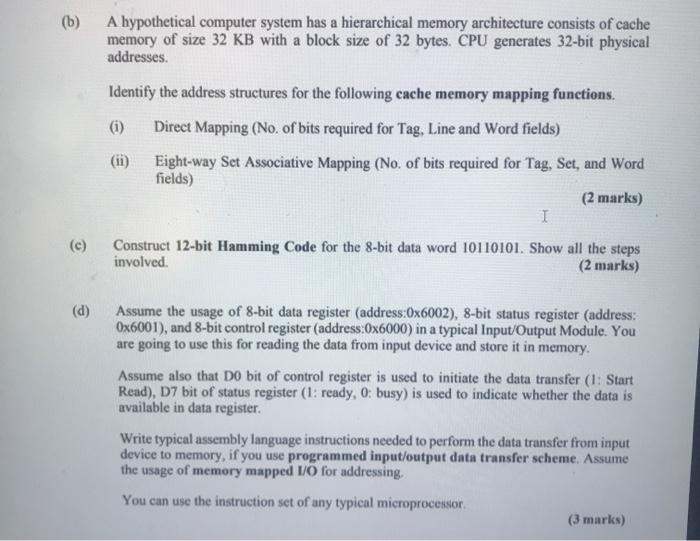

(b) A hypothetical computer system has a hierarchical memory architecture consists of cache memory of size 32 KB with a block size of 32 bytes. CPU generates 32-bit physical addresses. Identify the address structures for the following cache memory mapping functions. (1) Direct Mapping (No. of bits required for Tag, Line and Word fields) (ii) Eight-way Set Associative Mapping (No. of bits required for Tag, Set, and Word fields) (2 marks) I Construct 12-bit Hamming Code for the 8-bit data word 10110101. Show all the steps involved (2 marks) (d) Assume the usage of 8-bit data register (address:Ox6002), 8-bit status register (address: 0x6001), and 8-bit control register (address:Ox6000) in a typical Input/Output Module. You are going to use this for reading the data from input device and store it in memory. Assume also that Do bit of control register is used to initiate the data transfer (1: Start Read), D7 bit of status register (1 : ready, 0: busy) is used to indicate whether the data is available in data register Write typical assembly language instructions needed to perform the data transfer from input device to memory, if you use programmed input/output data transfer scheme. Assume the usage of memory mapped 1/0 for addressing You can use the instruction set of any typical microprocessor

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts