Question: Computer Architecture problem. Assuming Full-forwarding for all questions in this problem, consider the instruction sequence given below: LW R1, 8 (R1) ADD R1, R1, R2

Computer Architecture problem.

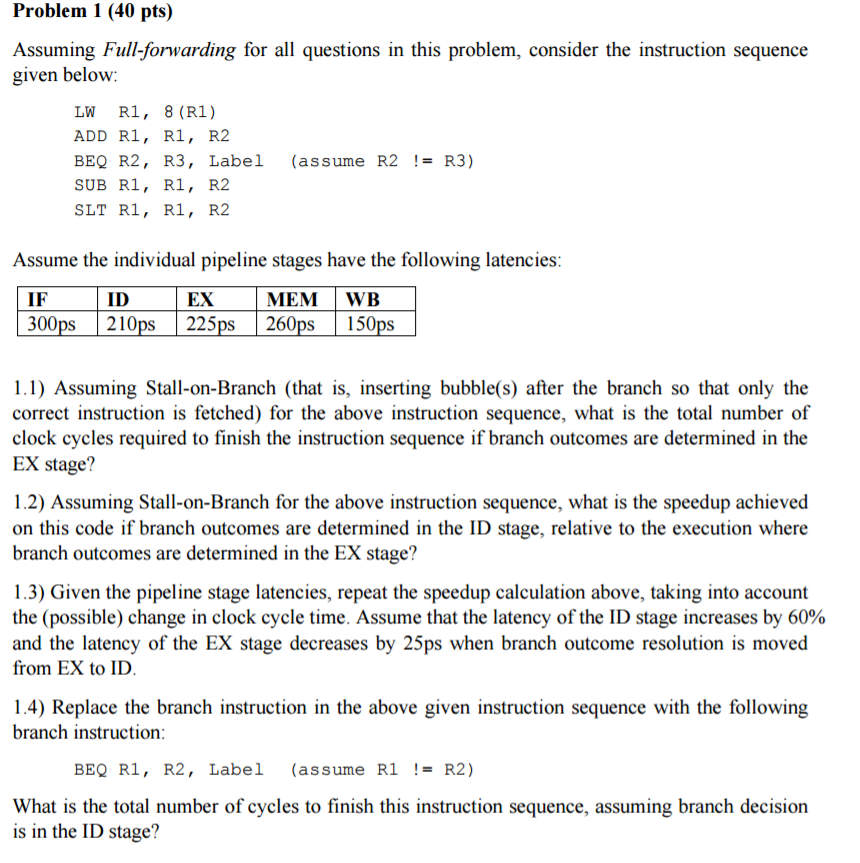

Assuming Full-forwarding for all questions in this problem, consider the instruction sequence given below: LW R1, 8 (R1) ADD R1, R1, R2 BEQ R2, R3, Label (assume R2 ! = R3) SUB R1, R1 R2 SLUT R1, R1 R2 Assume the individual pipeline stages have the following latencies: Assuming Stall-on-Branch (that is, inserting bubble(s) after the branch so that only the correct instruction is fetched) for the above instruction sequence, what is the total number of clock cycles required to finish the instruction sequence if branch outcomes are determined in the EX stage? Assuming Stall-on-Branch for the above instruction sequence, what is the speedup achieved on this code if branch outcomes are determined in the ID stage, relative to the execution where branch outcomes are determined in the EX stage? Given the pipeline stage latencies, repeat the speedup calculation above, taking into account the (possible) change in clock cycle time. Assume that the latency of the ID stage increases by 60% and the latency of the Ex stage decreases by 25ps when branch outcome resolution is moved from Ex to ID. Replace the branch instruction in the above given instruction sequence with the following branch instruction BEQ R1, R2, Label (assume R1 ! = R2) What is the total number of cycles to finish this instruction sequence, assuming branch decision is in the ID stage

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts