Question: . Consider a 3-pracessor multiprncessor connected with a shared hus that has the following properties: (0) centralized shared memory accessible with the bus, ( snoping-based

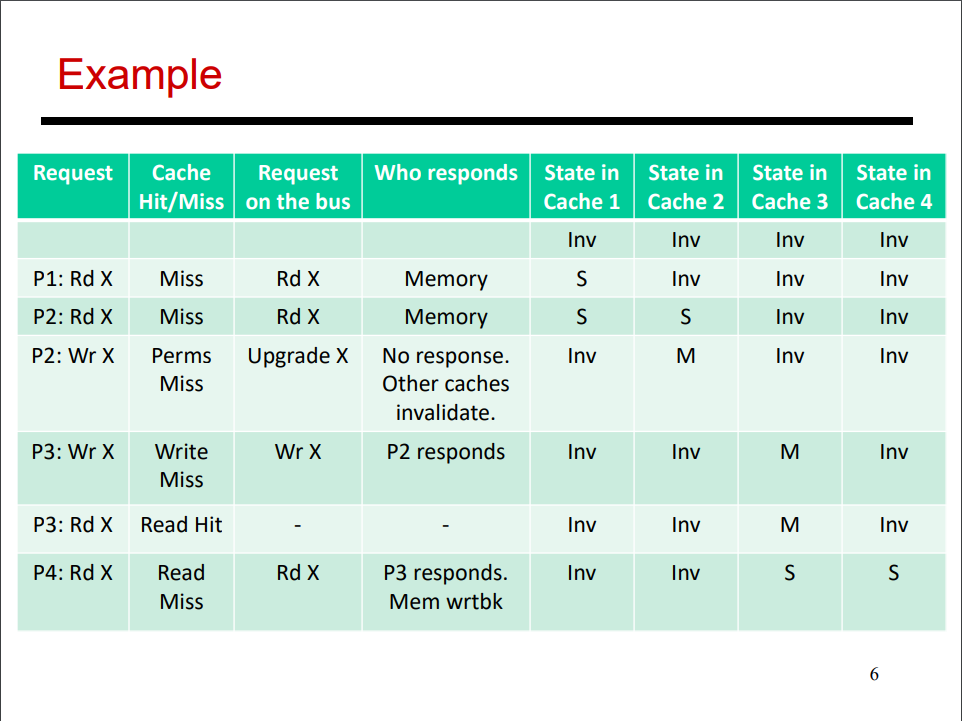

. Consider a 3-pracessor multiprncessor connected with a shared hus that has the following properties: (0) centralized shared memory accessible with the bus, ( snoping-based MSI ache coherence protocal, lii write-invalidate policy. Alsn assurme that the caches have a writebatk pulicy. Initially, the caches all have invalid dala. The processurs issue the following five requesls, one after the oter. Creale a lable similar to thal in slide 6 ul leclure 25lu indicale what happens for every request. (35 points) o P1: Read X P1:Write X o P3 Read X o P2: Read X a P3: Write X . Consider a 3-pracessor multiprncessor connected with a shared hus that has the following properties: (0) centralized shared memory accessible with the bus, ( snoping-based MSI ache coherence protocal, lii write-invalidate policy. Alsn assurme that the caches have a writebatk pulicy. Initially, the caches all have invalid dala. The processurs issue the following five requesls, one after the oter. Creale a lable similar to thal in slide 6 ul leclure 25lu indicale what happens for every request. (35 points) o P1: Read X P1:Write X o P3 Read X o P2: Read X a P3: Write X

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts