Question: Consider a basic in-order (single-issue) pipeline with bypassing (one instruction in each pipeline stage in any cycle). The pipeline has been extended to handle FP

Consider a basic in-order (single-issue) pipeline with bypassing (one instruction in each pipeline stage in any cycle). The pipeline has been extended to handle FP add. Assume the following latencies for the FP Add functional unit between dependent nstructions: o Load followed bv any instruction: 3 stall cvcles o FP ALU followed by any instruction (except stores): 5 stall cycles o FP ALU followed by store: 4 stall cycles o Int add followed by a branch: 2 stall cycles o Int add followed by any other instruction: 1 stall cycle o A conditional branch has 1 delay slot (where, an instruction is fetched in the cycle 3. after the branch without knowing the outcome of the branch, and is executed to completion) Below is the source code and the assembly code for a loop (40 points) Source Code: for (i-100; i>0; i--) 1 Assembly Code: Loop: L.D F1, O(R1) L.D F2, 0(R2) ADD.D F1, F2, F1 S.D F1, 0(R1) DADDUI RI, RI, #-8 DADDUI R2, R2, #-8 BNE R1, R3, Loojp NOP // Get wi] // Get x[i] // Add two numbers // Store the result into w[i] // Decrement R:1 // Decrement R.2 // Check if we've reached the end of the loop a. Show how the loop would look for unscheduled execution by the compiler (default schedule) (use a table to show the cycle at which an instruction is issued) for the default code. (10 points) Consider a basic in-order (single-issue) pipeline with bypassing (one instruction in each pipeline stage in any cycle). The pipeline has been extended to handle FP add. Assume the following latencies for the FP Add functional unit between dependent nstructions: o Load followed bv any instruction: 3 stall cvcles o FP ALU followed by any instruction (except stores): 5 stall cycles o FP ALU followed by store: 4 stall cycles o Int add followed by a branch: 2 stall cycles o Int add followed by any other instruction: 1 stall cycle o A conditional branch has 1 delay slot (where, an instruction is fetched in the cycle 3. after the branch without knowing the outcome of the branch, and is executed to completion) Below is the source code and the assembly code for a loop (40 points) Source Code: for (i-100; i>0; i--) 1 Assembly Code: Loop: L.D F1, O(R1) L.D F2, 0(R2) ADD.D F1, F2, F1 S.D F1, 0(R1) DADDUI RI, RI, #-8 DADDUI R2, R2, #-8 BNE R1, R3, Loojp NOP // Get wi] // Get x[i] // Add two numbers // Store the result into w[i] // Decrement R:1 // Decrement R.2 // Check if we've reached the end of the loop a. Show how the loop would look for unscheduled execution by the compiler (default schedule) (use a table to show the cycle at which an instruction is issued) for the default code. (10 points)

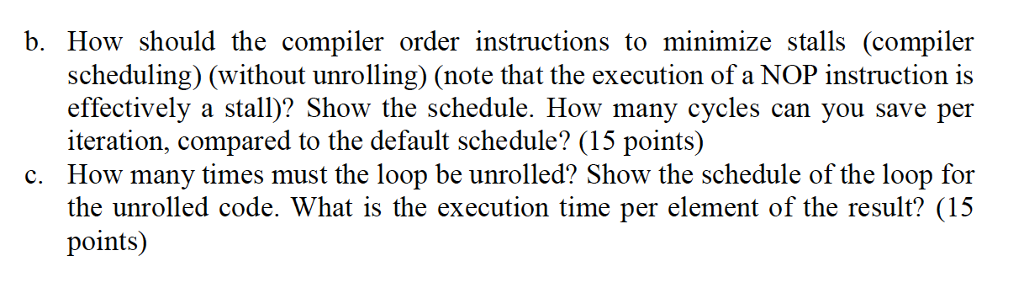

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts