Question: Consider a situation in which four processors in an SMP configuration, over time, require access to the same line of data from main memory. All

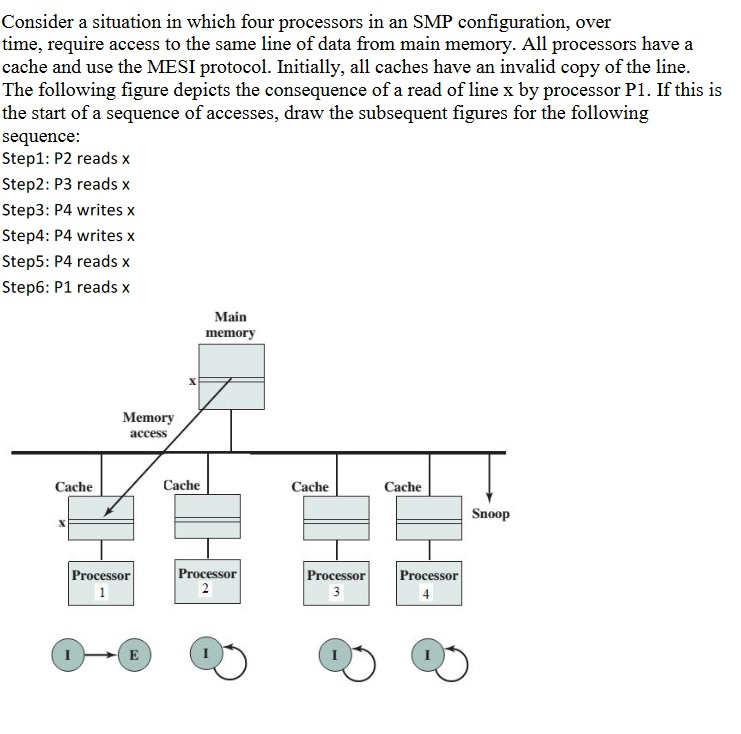

Consider a situation in which four processors in an SMP configuration, over time, require access to the same line of data from main memory. All processors have a cache and use the MESI protocol. Initially, all caches have an invalid copy of the line The following figure depicts the consequence of a read of line x by processor P1. If this is the start of a sequence of accesses, draw the subsequent figures for the following sequence Step1: P2 reads x Step2: P3 reads x Step3: P4 writes x Step4: P4 writes x Step5: P4 reads x Step6: P1 reads x Main memor Memory access Cache Cache Cache Cache Snoop Processor Processor Processor r Processor Consider a situation in which four processors in an SMP configuration, over time, require access to the same line of data from main memory. All processors have a cache and use the MESI protocol. Initially, all caches have an invalid copy of the line The following figure depicts the consequence of a read of line x by processor P1. If this is the start of a sequence of accesses, draw the subsequent figures for the following sequence Step1: P2 reads x Step2: P3 reads x Step3: P4 writes x Step4: P4 writes x Step5: P4 reads x Step6: P1 reads x Main memor Memory access Cache Cache Cache Cache Snoop Processor Processor Processor r Processor

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts