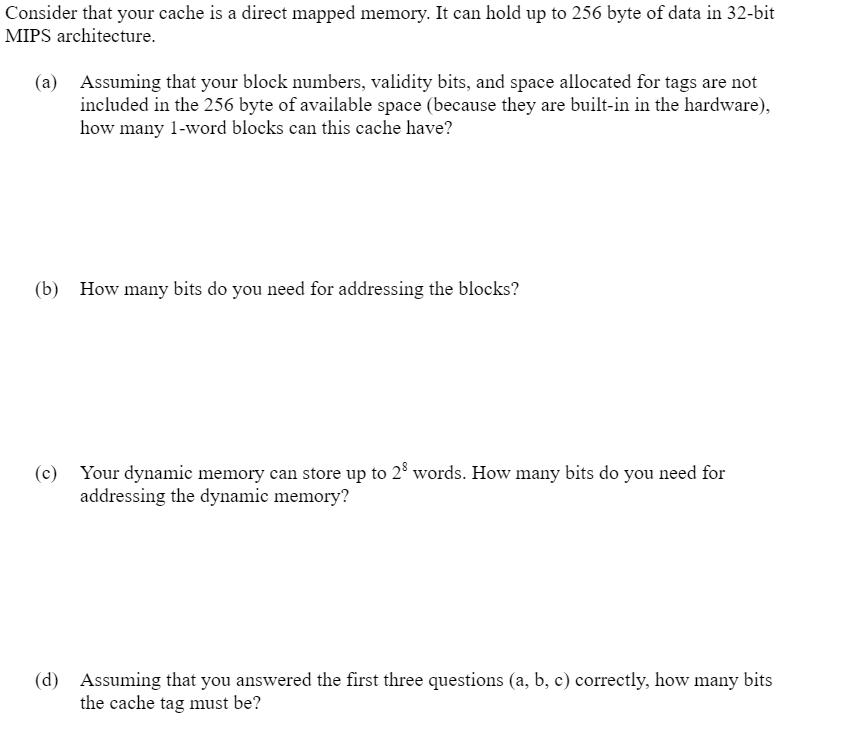

Question: Consider that your cache is a direct mapped memory. It can hold up to 256 byte of data in 32-bit MIPS architecture. (a) Assuming

Consider that your cache is a direct mapped memory. It can hold up to 256 byte of data in 32-bit MIPS architecture. (a) Assuming that your block numbers, validity bits, and space allocated for tags are not included in the 256 byte of available space (because they are built-in in the hardware), how many 1-word blocks can this cache have? (b) How many bits do you need for addressing the blocks? (c) Your dynamic memory can store up to 28 words. How many bits do you need for addressing the dynamic memory? (d) Assuming that you answered the first three questions (a, b, c) correctly, how many bits the cache tag must be?

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts