Question: Consider the code executed on a 5-stage MIPS pipeline (IF, ID, EX, MEM, WB) and assume that R2 value is preloaded as 396. Loop: LD

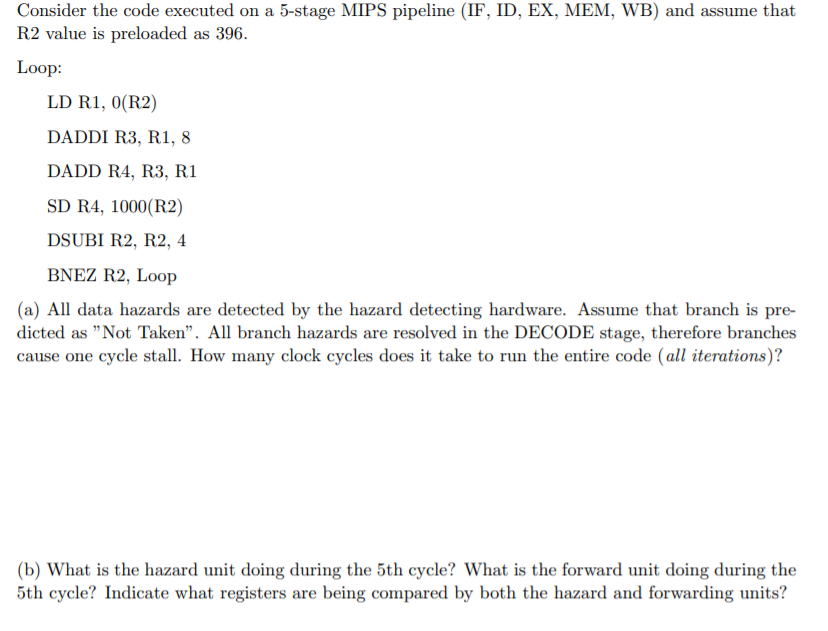

Consider the code executed on a 5-stage MIPS pipeline (IF, ID, EX, MEM, WB) and assume that R2 value is preloaded as 396. Loop: LD R1, 0(R2) DADDI R3, R1, 8 DADD R4, R3, R1 SD R4, 1000(R2) DSUBI R2, R2, 4 BNEZ R2, Loop (a) All data hazards are detected by the hazard detecting hardware. Assume that branch is pre- dicted as Not Taken. All branch hazards are resolved in the DECODE stage, therefore branches cause one cycle stall. How many clock cycles does it take to run the entire code (all iterations)? (b) What is the hazard unit doing during the 5th cycle? What is the forward unit doing during the 5th cycle? Indicate what registers are being compared by both the hazard and forwarding units? Consider the code executed on a 5-stage MIPS pipeline (IF, ID, EX, MEM, WB) and assume that R2 value is preloaded as 396. Loop: LD R1, 0(R2) DADDI R3, R1, 8 DADD R4, R3, R1 SD R4, 1000(R2) DSUBI R2, R2, 4 BNEZ R2, Loop (a) All data hazards are detected by the hazard detecting hardware. Assume that branch is pre- dicted as Not Taken. All branch hazards are resolved in the DECODE stage, therefore branches cause one cycle stall. How many clock cycles does it take to run the entire code (all iterations)? (b) What is the hazard unit doing during the 5th cycle? What is the forward unit doing during the 5th cycle? Indicate what registers are being compared by both the hazard and forwarding units

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts