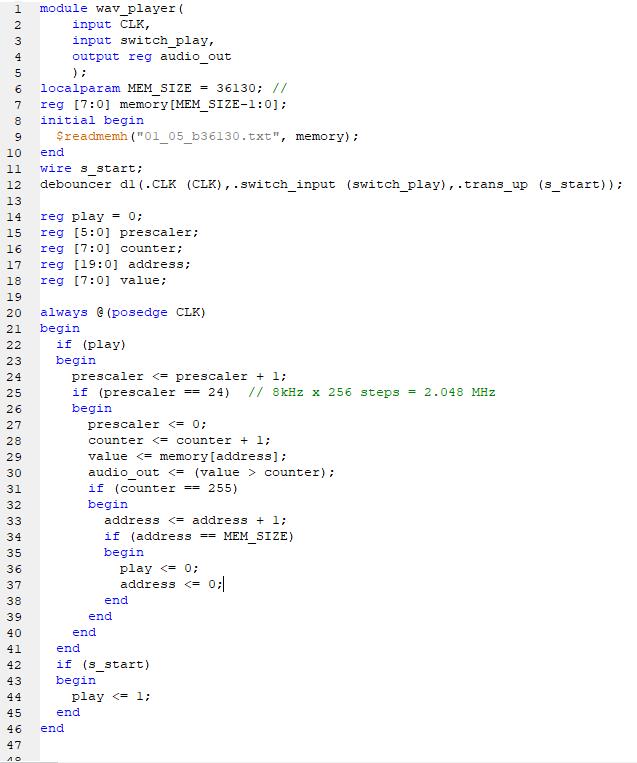

Question: Convert the code from Verilog to Vhdl module wav_player input CLK, input switch_play, output reg audio_out ); localparam MEM_SIZE = 36130; // reg (7:0) memory

Convert the code from Verilog to Vhdl

module wav_player input CLK, input switch_play, output reg audio_out ); localparam MEM_SIZE = 36130; // reg (7:0) memory [MEM_SIZE-1:0]; initial begin Sreadmem ("01_05_b36130.txt", memory); end wire s_start; debouncer dl(.CLK (CLK), switch_input (switch_play), .trans_up (s_start)); reg play = 0; reg (5:0] prescaler; reg [7:0] counter; reg (19:0] address; reg (7:0) value; 1 2 3 4 5 6 7 8 9 10 ll 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 NNNNNNNNNN mm 0 0 O 000 always @ (posedge CLK) begin if (play) begin prescaler counter); if (counter == 255) begin address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts