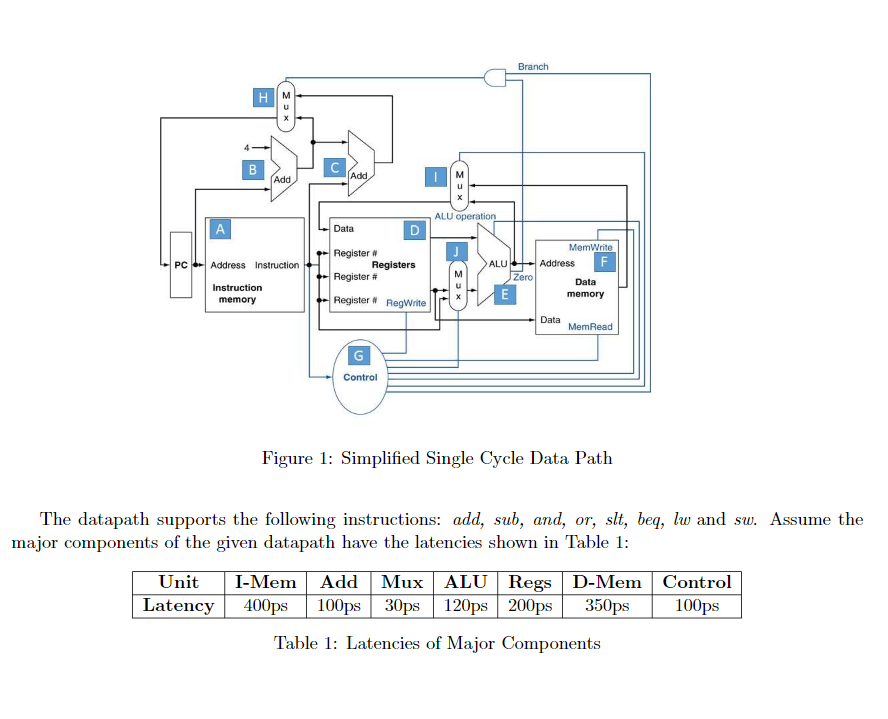

Question: Data D Register # Register # Register # RegWrite MemWrite PCAddress Instruction Registers Data MemRead Control Figure 1: Simplified Single Cycle Data Path The datapath

Data D Register # Register # Register # RegWrite MemWrite PCAddress Instruction Registers Data MemRead Control Figure 1: Simplified Single Cycle Data Path The datapath supports the following instructions: add, sub, and, or, slt, beq, lw and sw. Assume the major components of the given datapath have the latencies shown in Table 1: UnitI-Mem AddM Mux ALURegs D-Mem Control Latency400ps100ps30ps 120ps 200ps 350ps100ps Table 1: Latencies of Major Components Data D Register # Register # Register # RegWrite MemWrite PCAddress Instruction Registers Data MemRead Control Figure 1: Simplified Single Cycle Data Path The datapath supports the following instructions: add, sub, and, or, slt, beq, lw and sw. Assume the major components of the given datapath have the latencies shown in Table 1: UnitI-Mem AddM Mux ALURegs D-Mem Control Latency400ps100ps30ps 120ps 200ps 350ps100ps Table 1: Latencies of Major Components

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts