Question: Please help. Will give thumbs up. Question 2. Consider the data path shown in Figure 4.2. Assume that the components have the following latencies in

Please help. Will give thumbs up.

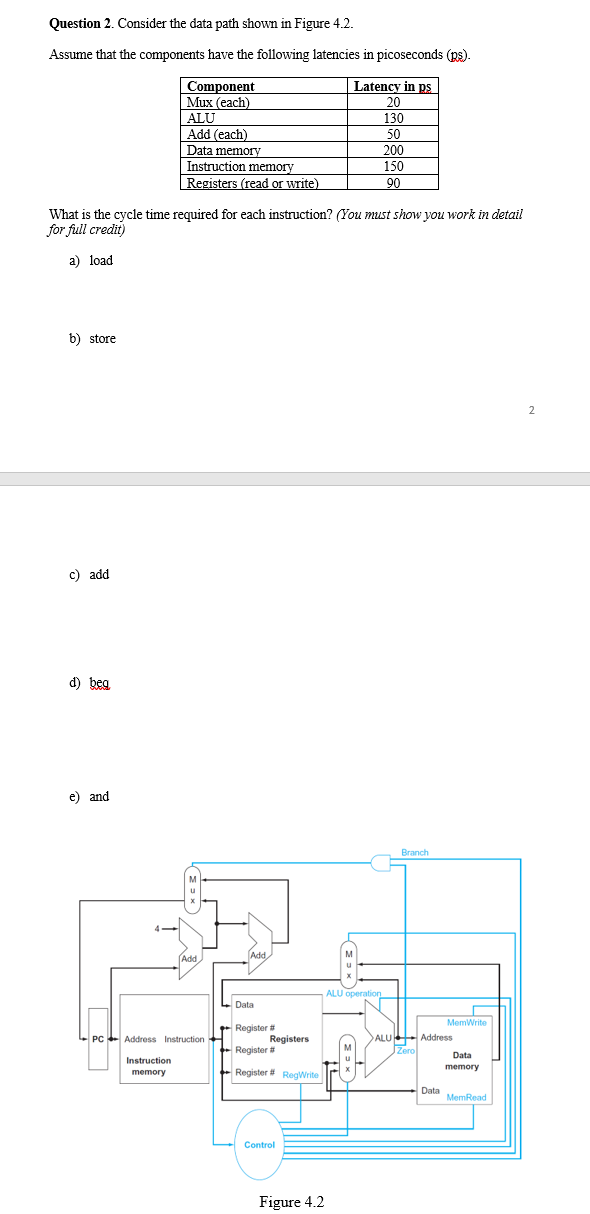

Question 2. Consider the data path shown in Figure 4.2. Assume that the components have the following latencies in picoseconds (Rs). Component Latency in ps Mux (each) 20 ALU 130 Add (each) 50 Data memory 200 Instruction memory 150 Registers (read or write) 90 What is the cycle time required for each instruction? (You must show you work in detail for full credit) a) load b) store 2 c) add d) beg e) and Branch Add Add M ALU operation Data PC Address Instruction 4 Register Registers Register M MemWrite > ALUL Address Zero Data memory Instruction memory Register # RegWrite Data MemRead Control Figure 4.2 Question 2. Consider the data path shown in Figure 4.2. Assume that the components have the following latencies in picoseconds (Rs). Component Latency in ps Mux (each) 20 ALU 130 Add (each) 50 Data memory 200 Instruction memory 150 Registers (read or write) 90 What is the cycle time required for each instruction? (You must show you work in detail for full credit) a) load b) store 2 c) add d) beg e) and Branch Add Add M ALU operation Data PC Address Instruction 4 Register Registers Register M MemWrite > ALUL Address Zero Data memory Instruction memory Register # RegWrite Data MemRead Control Figure 4.2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts