Question: Design a 5-stage pipeline mini-MIPS processor to execute the instruciton lw $t3, 0xFFF4($t0). Answer following questions when it executes lw $t3, 0xFFF4($t0) 1. draw the

Design a 5-stage pipeline mini-MIPS processor to execute the instruciton lw $t3, 0xFFF4($t0).

Answer following questions when it executes lw $t3, 0xFFF4($t0)

1. draw the complete microarchitecture of the 5-stage pipeline

mini-MIPS processor datapath and control signals needed to execute

this instruction.

2. Describe in words how the datapath works in each stage in executing this instruction

3. Describe in words how the control signals work in each stage in executing this instruction

4. Describe in words values of each control signal in executing this instruction

5. Describe in words which stage contains the critical path of the datapath, and explain how to compute the cycle time by giving a formular.

**Please answer it clearly one by one (Answer as most as you can or else if I have to post another post to complete the question please let me know . Thank you)

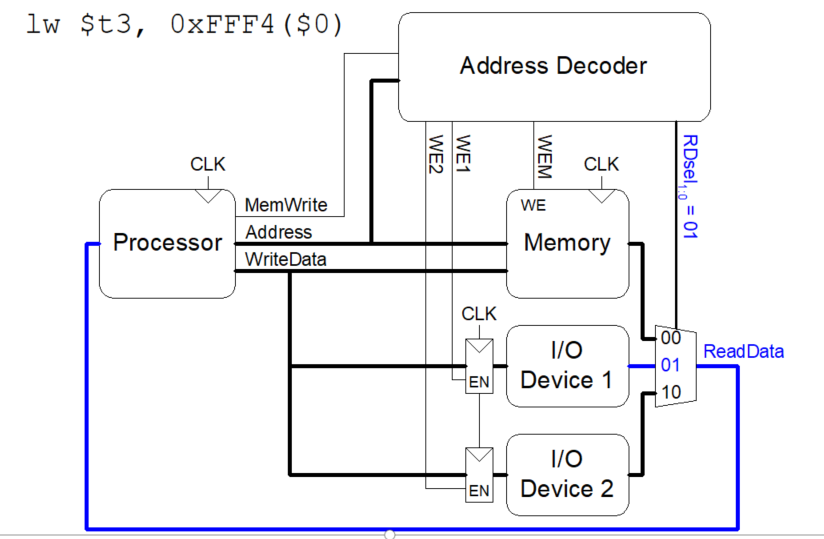

lw $t3, OxFFF4 ($0) Address Decoder CLK WE2 WE1 WEM CLK RDsel:0 = 01 WE Processor Mem Write Address Write Data Memory CLK Read Data I/O Device 1 00 01 10 EN I/O Device 2 EN

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts