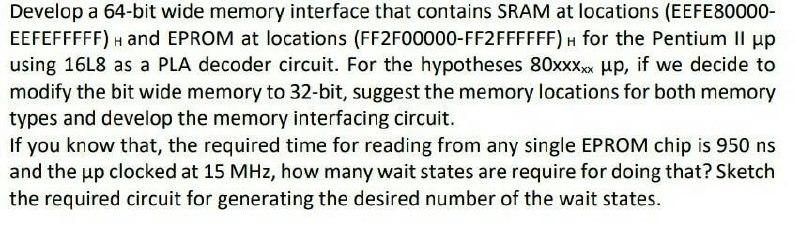

Question: Develop a 64-bit wide memory interface that contains SRAM at locations (EEFE80000- EEFEFFFFF) H and EPROM at locations (FF2F00000-FF2FFFFFF) H for the Pentium II up

Develop a 64-bit wide memory interface that contains SRAM at locations (EEFE80000- EEFEFFFFF) H and EPROM at locations (FF2F00000-FF2FFFFFF) H for the Pentium II up using 16L8 as a PLA decoder circuit. For the hypotheses 80xxXxx up, if we decide to modify the bit wide memory to 32-bit, suggest the memory locations for both memory types and develop the memory interfacing circuit. If you know that, the required time for reading from any single EPROM chip is 950 ns and the up clocked at 15 MHz, how many wait states are require for doing that? Sketch the required circuit for generating the desired number of the wait states. Develop a 64-bit wide memory interface that contains SRAM at locations (EEFE80000- EEFEFFFFF) H and EPROM at locations (FF2F00000-FF2FFFFFF) H for the Pentium II up using 16L8 as a PLA decoder circuit. For the hypotheses 80xxXxx up, if we decide to modify the bit wide memory to 32-bit, suggest the memory locations for both memory types and develop the memory interfacing circuit. If you know that, the required time for reading from any single EPROM chip is 950 ns and the up clocked at 15 MHz, how many wait states are require for doing that? Sketch the required circuit for generating the desired number of the wait states

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts