Question: ECEN 3734 - Computer Design Problem: Based on the given VHDL codes... (a) Complete the ModelSim force commands to perform the given (shown below) calculations.

ECEN 3734 - Computer Design

Problem: Based on the given VHDL codes...

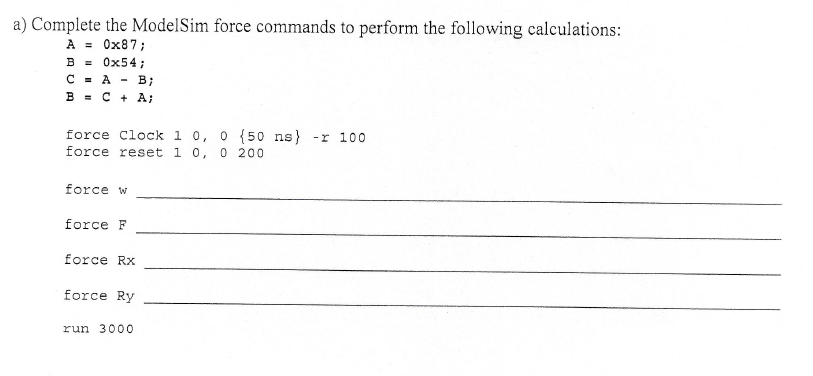

(a) Complete the ModelSim force commands to perform the given (shown below) calculations.

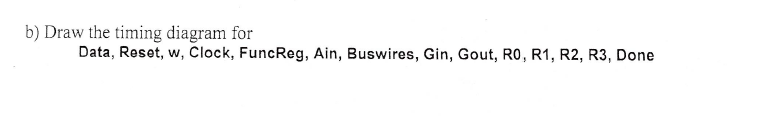

(b) Draw the timing diagram for the following: Data, Reset, w, Clock, FuncReg, Ain, BusWires, Gin, Gout, R0, R1, R2, R3, Done

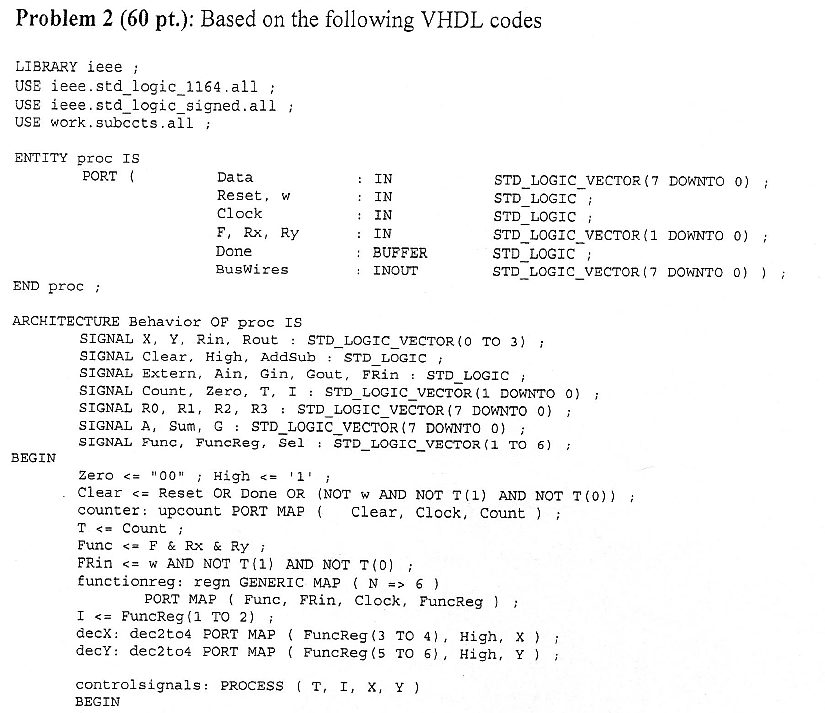

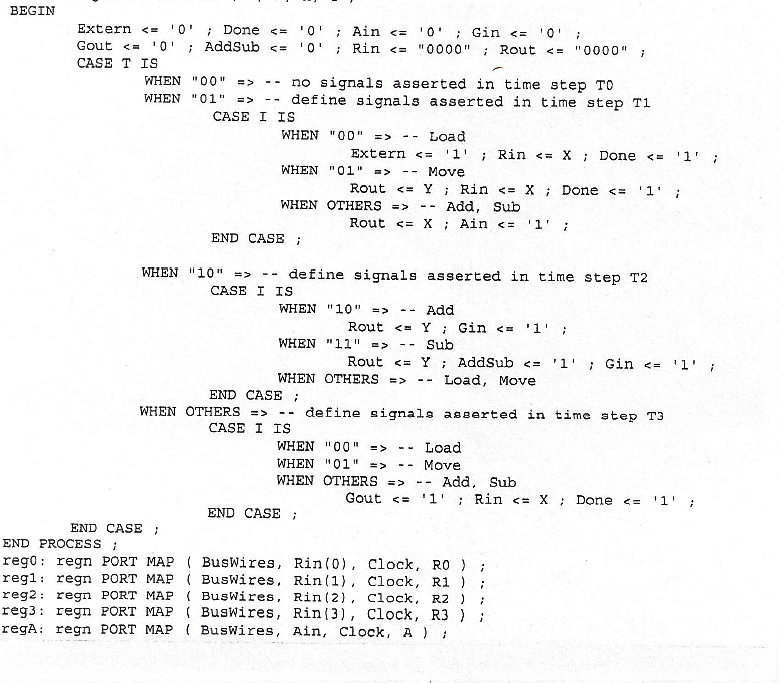

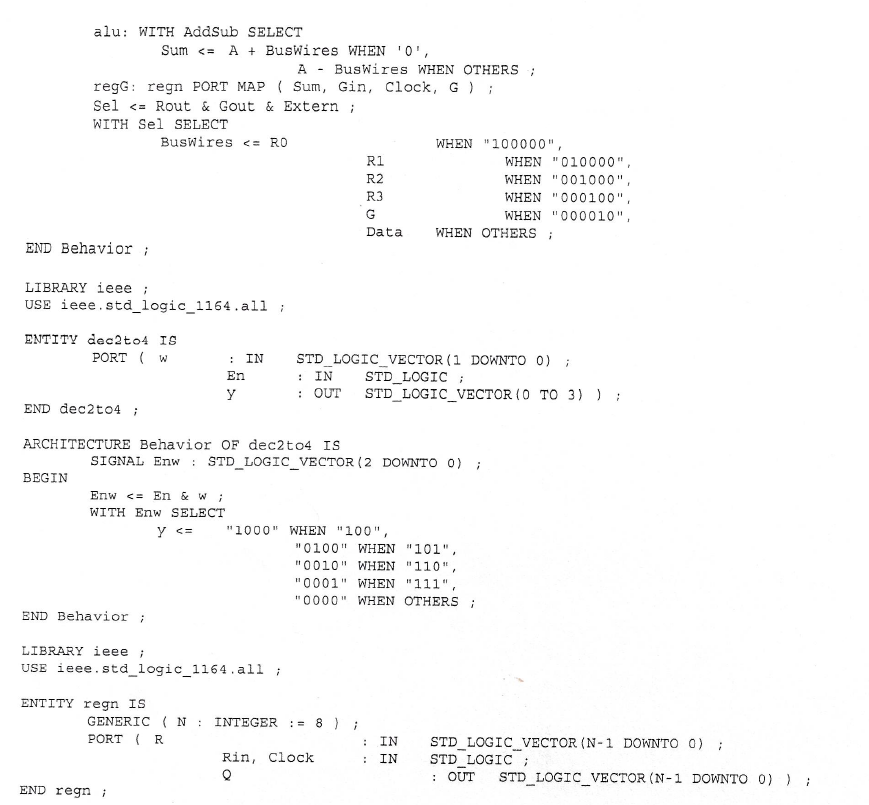

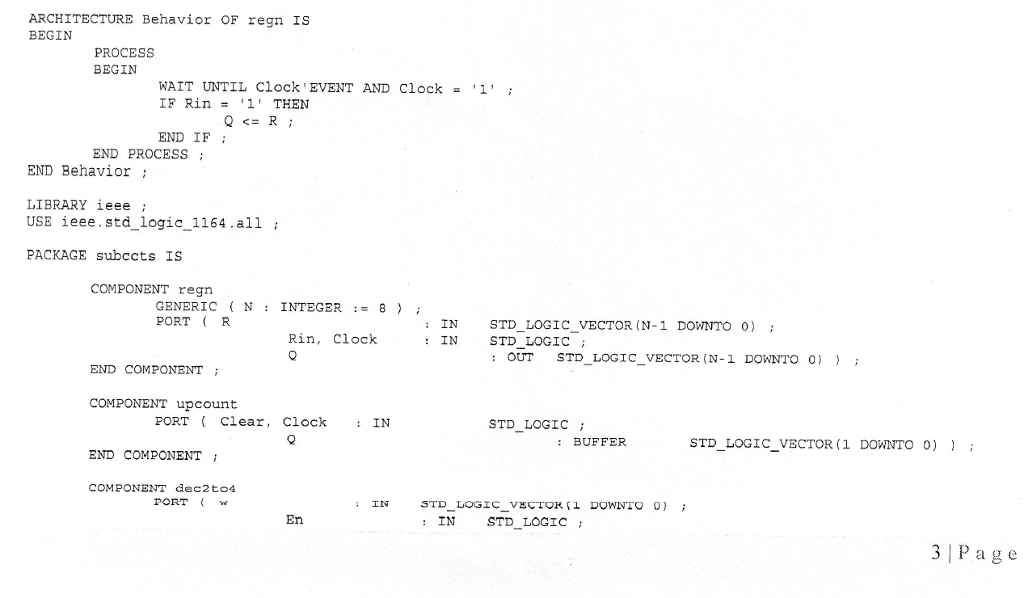

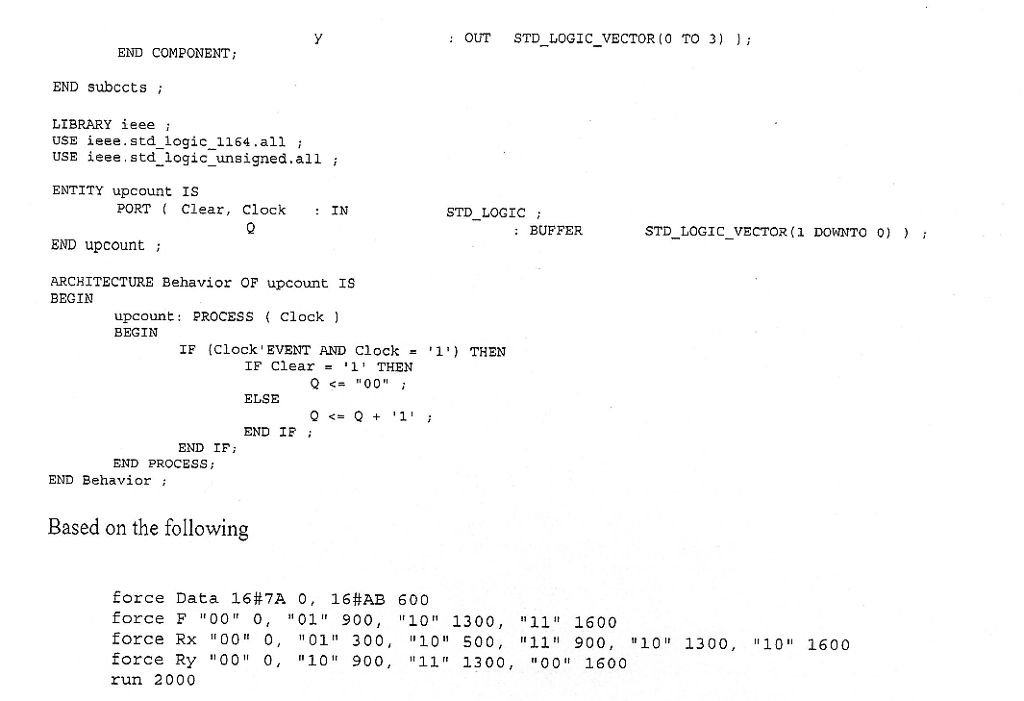

Problem 2 (60 pt.): Based on the following VHDL codes LIBRARY ieee ; USE ieee.std_logic 1164.all; USE ieee.std logic signed.alli USE work.subccts.all ENTITY proc IS PORT Data Reset, W Clock F, Rx, Ry Done BusWires STD LOGIC VECTOR (7 DOWNTO 0) STD LOGIC STD_LOGIC STD LOGIC_VECTOR (1 DOWNTO 0) STD LOGIC STD LOGIC_VECTOR (7 DOWNTO 0)) : BUFFER : INOUT END proc ARCHITECTURE Behavior OF proc IS SIGNAL X, Y, Rin, Rout STD_LOGIC_VECTOR (O TO 3)i SIGNAL Clear, High, AddSub STD LOGIC SIGNAL Extern, Ain, Gin, Gout, FRin STD_LOGICi SIGNAL Count, Zero, T, ISTD LOGIC VECTOR(1 DOWNTO 0) i SIGNAL RO, R1, R2, R3 STD_ LOGIC_VECTOR (7 DOWNTO 0)i SIGNAL A, Sum, G STD_LOGIC_VECTOR(7 DOWNTO 0) SIGNAL Func, FuncReg, Sel : STD LOGIC_VECTOR (1 TO 6 ; BEGIN Clea r Reset OR Done OR (NOT w AND NOT T (1) AND NOT T(O) counter: upcount PORT MAP Clear, Clock, Count T 6 PORT MAP Func, FRin, Clock, FuncReg 1FuncReg (1 TO 2) decX dec2to4 PORT MAP ( FuncReg (3 TO 4), High, Xi decY: dec2to4 PORT MAP ( FuncReg (5 TO 6) , High, Y) ; control signals: PROCESS T, 1, X, Y ) BEGIN Problem 2 (60 pt.): Based on the following VHDL codes LIBRARY ieee ; USE ieee.std_logic 1164.all; USE ieee.std logic signed.alli USE work.subccts.all ENTITY proc IS PORT Data Reset, W Clock F, Rx, Ry Done BusWires STD LOGIC VECTOR (7 DOWNTO 0) STD LOGIC STD_LOGIC STD LOGIC_VECTOR (1 DOWNTO 0) STD LOGIC STD LOGIC_VECTOR (7 DOWNTO 0)) : BUFFER : INOUT END proc ARCHITECTURE Behavior OF proc IS SIGNAL X, Y, Rin, Rout STD_LOGIC_VECTOR (O TO 3)i SIGNAL Clear, High, AddSub STD LOGIC SIGNAL Extern, Ain, Gin, Gout, FRin STD_LOGICi SIGNAL Count, Zero, T, ISTD LOGIC VECTOR(1 DOWNTO 0) i SIGNAL RO, R1, R2, R3 STD_ LOGIC_VECTOR (7 DOWNTO 0)i SIGNAL A, Sum, G STD_LOGIC_VECTOR(7 DOWNTO 0) SIGNAL Func, FuncReg, Sel : STD LOGIC_VECTOR (1 TO 6 ; BEGIN Clea r Reset OR Done OR (NOT w AND NOT T (1) AND NOT T(O) counter: upcount PORT MAP Clear, Clock, Count T 6 PORT MAP Func, FRin, Clock, FuncReg 1FuncReg (1 TO 2) decX dec2to4 PORT MAP ( FuncReg (3 TO 4), High, Xi decY: dec2to4 PORT MAP ( FuncReg (5 TO 6) , High, Y) ; control signals: PROCESS T, 1, X, Y ) BEGIN

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts