Question: EE222 DIGITAL DESIGN LABORATORY EXPERIMENT - 5 Seven Segment Display Procedure: 1. Implement the code given below and understand working principle of seven segment display.

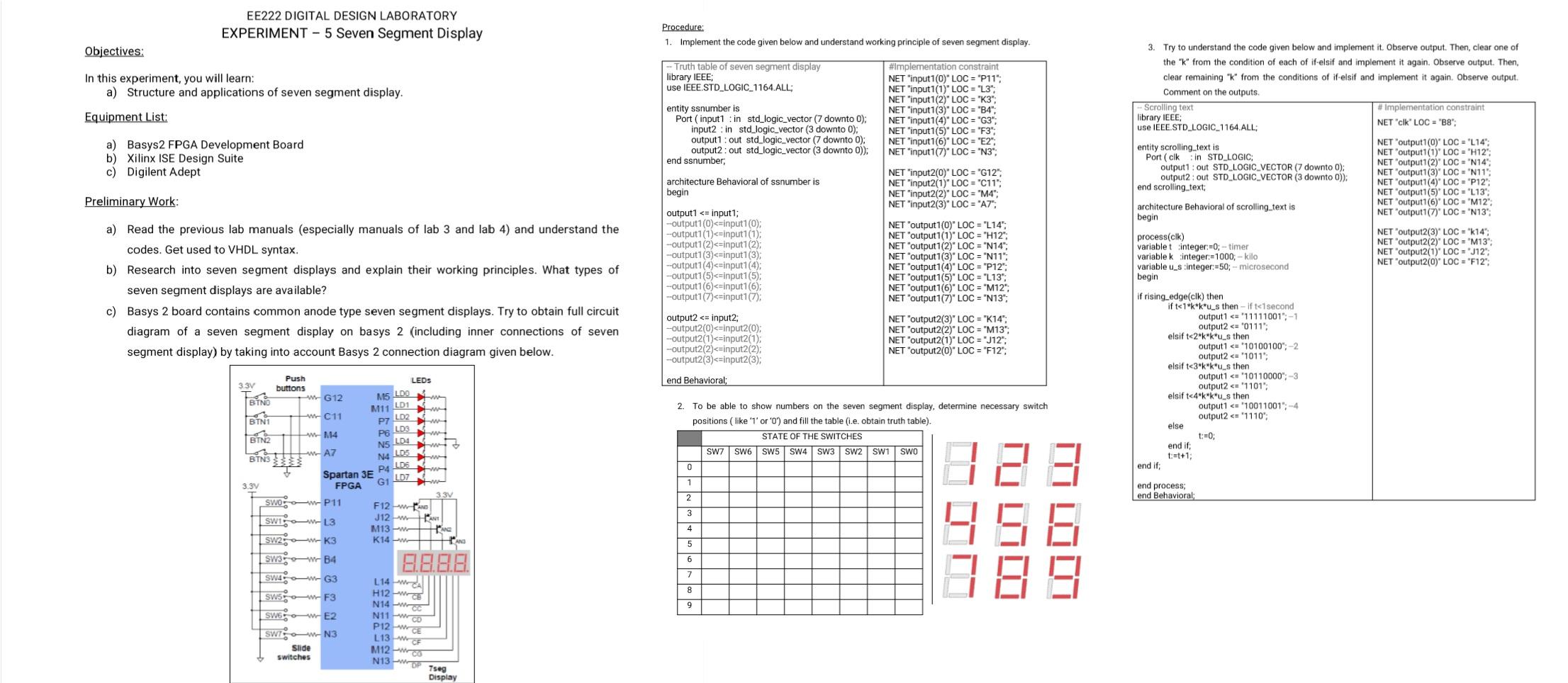

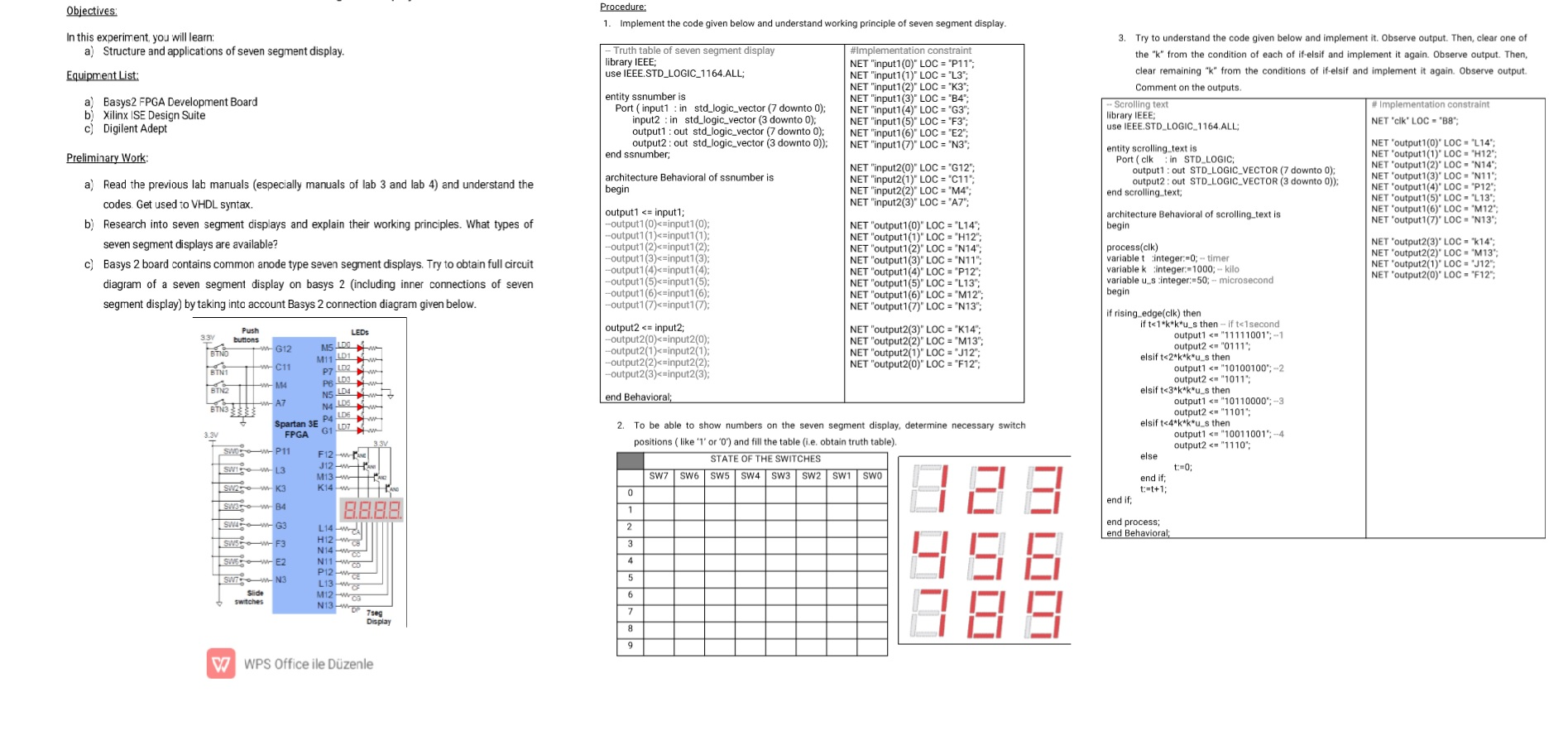

EE222 DIGITAL DESIGN LABORATORY EXPERIMENT - 5 Seven Segment Display Procedure: 1. Implement the code given below and understand working principle of seven segment display. Objectives: Truth table of seven segment display library IEEE; use IEEE.STD_LOGIC_1164.ALL: In this experiment, you will learn: a) Structure and applications of seven segment display. Equipment List: entity ssnumber is Port (input1 : in std_logic_vector (7 downto 0); input2 : in std_logic_vector (3 downto 0); output1: out std_logic_vector (7 downto 0); output2: out std_logic_vector (3 downto 0)); end ssnumber; #Implementation constraint NET "input1(0)" LOC = "P11"; NET"input1(1)"LOC = "L3", NET "input1(2)" LOC = "K3"; NET "input1(3)" LOC = "B4"; NET "input1(4)" LOC = "G3", NET "input1(5)" LOC = "F3", NET "input1(6)"LOC = 'E2"; NET "input1 (7)" LOC = "N3"; a) Basys 2 FPGA Development Board b) Xilinx ISE Design Suite c) Digilent Adept 3. Try to understand the code given below and implement it. Observe output. Then, clear one of the "k" from the condition of each of if-elsif and implement it again. Observe output. Then, clear remaining "k" from the conditions of if-elsif and implement it again. Observe output. Comment on the outputs. Scrolling text # Implementation constraint library IEEE; use IEEE.STD_LOGIC_1164.ALL: NET 'clk'LOC = "18"; entity scrolling_text is NET 'output(0) LOC = "L14"; Port (clk in STD_LOGIC; NET 'output1(1) LOC = "H12"; output1: out STD_LOGIC VECTOR (7 downto 0); NET "output1(2) LOC = 'N14", output2: out STD_LOGIC_VECTOR (3 downto 0)); NET "output(3) LOC = 'N11"; end scrolling text: NET "output1 (4) LOC = "P12" NET "output1 (5) LOC = "L13", architecture Behavioral of scrolling text is NET "output1 (6) LOC="M12"; begin NET"output 1(7) LOC = 'N13", process(clk) NET 'output2(3) LOC = "14"; variablet integer: 0; -timer NET "output2(2) LOC = "M13"; variable k integer:=1000,- kilo NET 'output2(1) LOC = 'J12"; variable u_s :integer;=50; -- microsecond NET "output2(0) LOC = "F12", begin architecture Behavioral of ssnumber is begin Preliminary Work: a) Read the previous lab manuals (especially manuals of lab 3 and lab 4) and understand the codes. Get used to VHDL syntax. b) Research into seven segment displays and explain their working principles. What types of seven segment displays are available? c) Basys 2 board contains common anode type seven segment displays. Try to obtain full circuit diagram of a seven segment display on basys 2 (including inner connections of seven segment display) by taking into account Basys 2 connection diagram given below. output1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts