Question: Email me the answer, Thanks!! 17. Consider the following sequence of memory references in a 16-bit processor Address (hex) Type A000 B000 A380 A004 5800

Email me the answer, Thanks!!

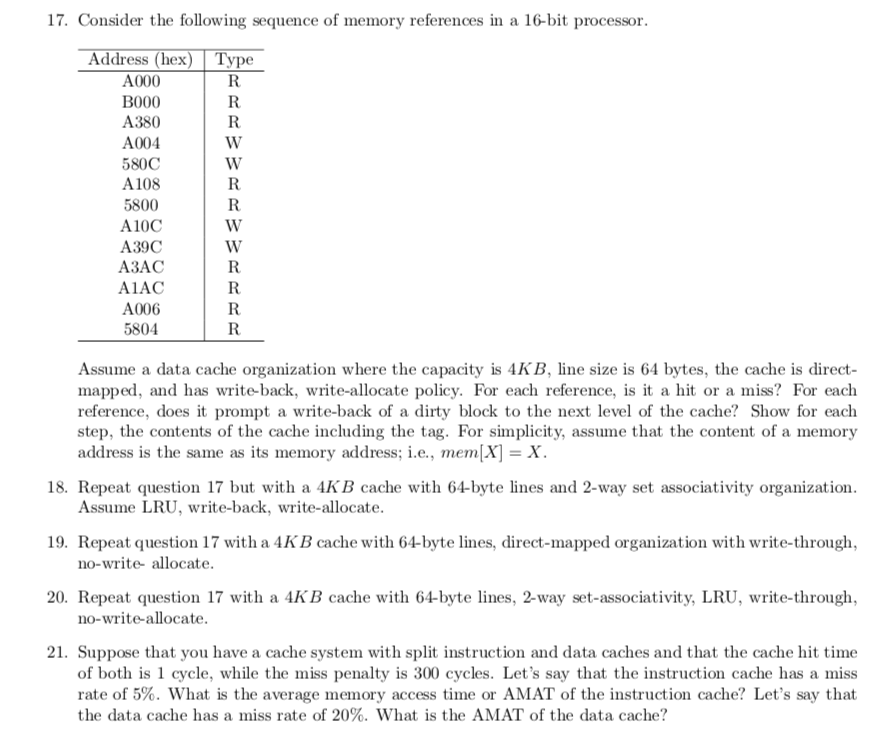

17. Consider the following sequence of memory references in a 16-bit processor Address (hex) Type A000 B000 A380 A004 5800 A108 5800 A10C A39C ???? A1AC A006 5804 Assume a data cache organization where the capacity is 4KB, line size is 64 bytes, the cache is direct mapped, and has write-back, write-allocate policy. For each reference, is it a hit or a miss? For each reference, does it prompt a write-back of a dirty block to the next level of the cache? Show for each step, the contents of the cache including the tag. For simplicity, assume that the content of a memory address is the same as its memory address: i.e., mem(X) = X. 18. Repeat question 17 but with a 4KB cache with 64-byte lines and 2-way set associativity organization 19. Repeat question 17 with a 4KB cache with 64-byte lines, direct-mapped organization with write-through, 20. Repeat question 17 with a 4KB cache with 64-byte lines, 2-way set-associativity, LRU, write-through, Assume LRU, write-back, write-allocate. no-write- allocate no-write-allocate. Suppose that you have a cache system with split instruction and data caches and that the cache hit time of both is 1 cycle, while the miss penalty is 300 cycles. Let's say that the instruction cache has a miss rate of 5%. What is the average memory access time or AMAT of the instruction cache? Let's say that the data cache has a miss rate of 20%, what is the AMAT of the data cache? 21. 17. Consider the following sequence of memory references in a 16-bit processor Address (hex) Type A000 B000 A380 A004 5800 A108 5800 A10C A39C ???? A1AC A006 5804 Assume a data cache organization where the capacity is 4KB, line size is 64 bytes, the cache is direct mapped, and has write-back, write-allocate policy. For each reference, is it a hit or a miss? For each reference, does it prompt a write-back of a dirty block to the next level of the cache? Show for each step, the contents of the cache including the tag. For simplicity, assume that the content of a memory address is the same as its memory address: i.e., mem(X) = X. 18. Repeat question 17 but with a 4KB cache with 64-byte lines and 2-way set associativity organization 19. Repeat question 17 with a 4KB cache with 64-byte lines, direct-mapped organization with write-through, 20. Repeat question 17 with a 4KB cache with 64-byte lines, 2-way set-associativity, LRU, write-through, Assume LRU, write-back, write-allocate. no-write- allocate no-write-allocate. Suppose that you have a cache system with split instruction and data caches and that the cache hit time of both is 1 cycle, while the miss penalty is 300 cycles. Let's say that the instruction cache has a miss rate of 5%. What is the average memory access time or AMAT of the instruction cache? Let's say that the data cache has a miss rate of 20%, what is the AMAT of the data cache? 21

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts