Repeat Problem 12-1 for the following sequence of read addresses: 0, 4, 12, 8, 14, 1C, 1A,

Question:

Repeat Problem 12-1 for the following sequence of read addresses: 0, 4, 12, 8, 14, 1C, 1A, 28, 26, 2E, 36, 30, 3E 38, 46, 40, 4E, 48, 56, 50, 5E, 58.

Problem 12-1

A CPU produces the following sequence of read addresses in hexadecimal:

54, 58, 104, 5C, 108, 60, F0, 64, 54, 58, 10C, 5C, 110, 60, F0, 64.

Supposing that the cache is empty to begin with, and assuming an LRU replacement, determine whether each address produces a hit or a miss for each of the following caches:

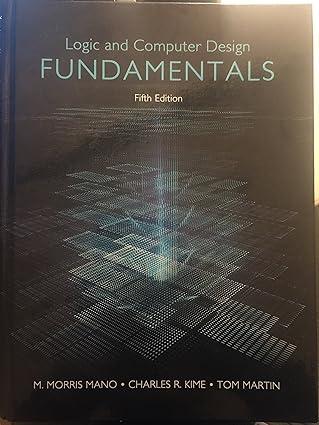

(a) direct mapped in Figure 12-3.

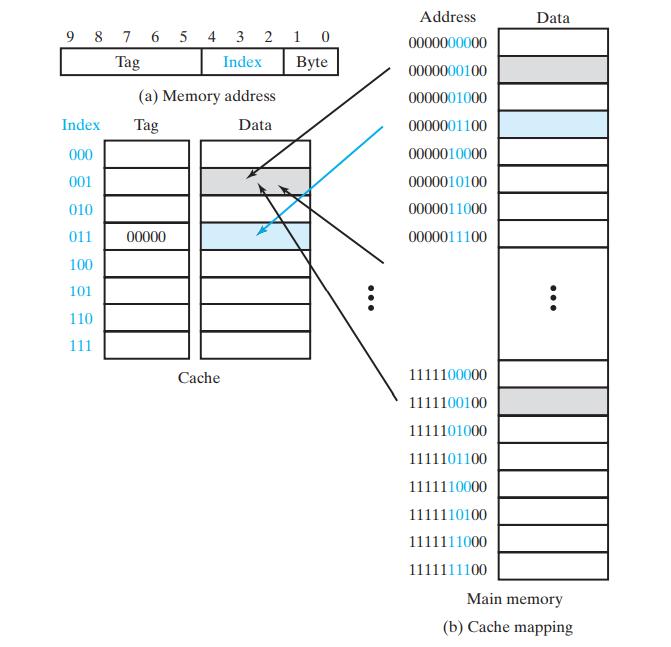

(b) fully associative in Figure 12-4.

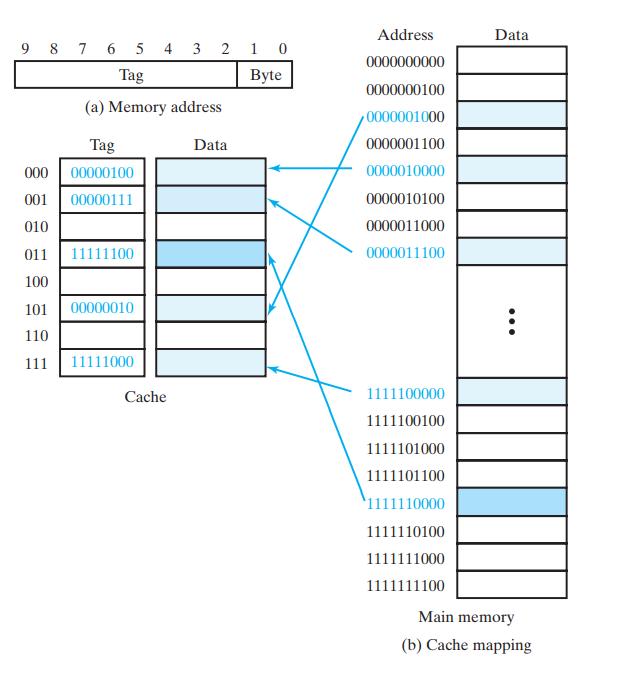

(c) two-way set associative in Figure 12-6.

Figure 12-3

Figure 12-4

Figure 12-6

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Logic And Computer Design Fundamentals

ISBN: 9780133760637

5th Edition

Authors: M. Morris Mano, Charles Kime, Tom Martin

Question Posted: