Question: exam please help!! Complete the below VHDL code of a N-bit (generic) parallel load up/down counter with Asynchronous reset The counter has the following inputs:

exam please help!!

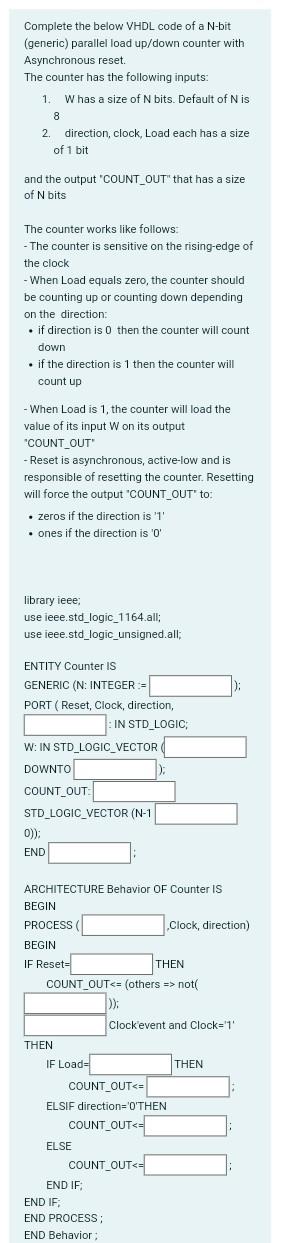

Complete the below VHDL code of a N-bit (generic) parallel load up/down counter with Asynchronous reset The counter has the following inputs: 1. W has a size of N bits. Default of N is 8 2. direction, clock, Load each has a size of 1 bit and the output 'COUNT_OUT" that has a size " a of N bits The counter works like follows: - The counter is sensitive on the rising-edge of the clock When Load equals zero, the counter should be counting up or counting down depending on the direction: . if direction is 0 then the counter will count down . if the direction is 1 then the counter will count up When Load is 1, the counter will load the value of its input W on its output "COUNT_OUT" - Reset is asynchronous, active-low and is responsible of resetting the counter. Resetting will force the output "COUNT_OUT' to: " zeros if the direction is '1' .ones if the direction is '0' O library ieee; ; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; ENTITY Counter IS GENERIC (N: INTEGER PORT (Reset, Clock, direction, :IN STD_LOGIC W: IN STD_LOGIC VECTOR DOWNTO COUNT_OUT STD_LOGIC_VECTOR (N-1 0)); END ARCHITECTURE Behavior Of Counter IS BEGIN PROCESS Clock, direction) BEGIN IF Reset THEN COUNT_OUT not )); D: Clock event and Clock='1' = THEN IF Load THEN COUNT_OUT

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts