Question: Example Memory access: 200 ps ALU and addition operations: 100 ps Register file access (read or write): 50 ps And assume other parts (multiplexors, control

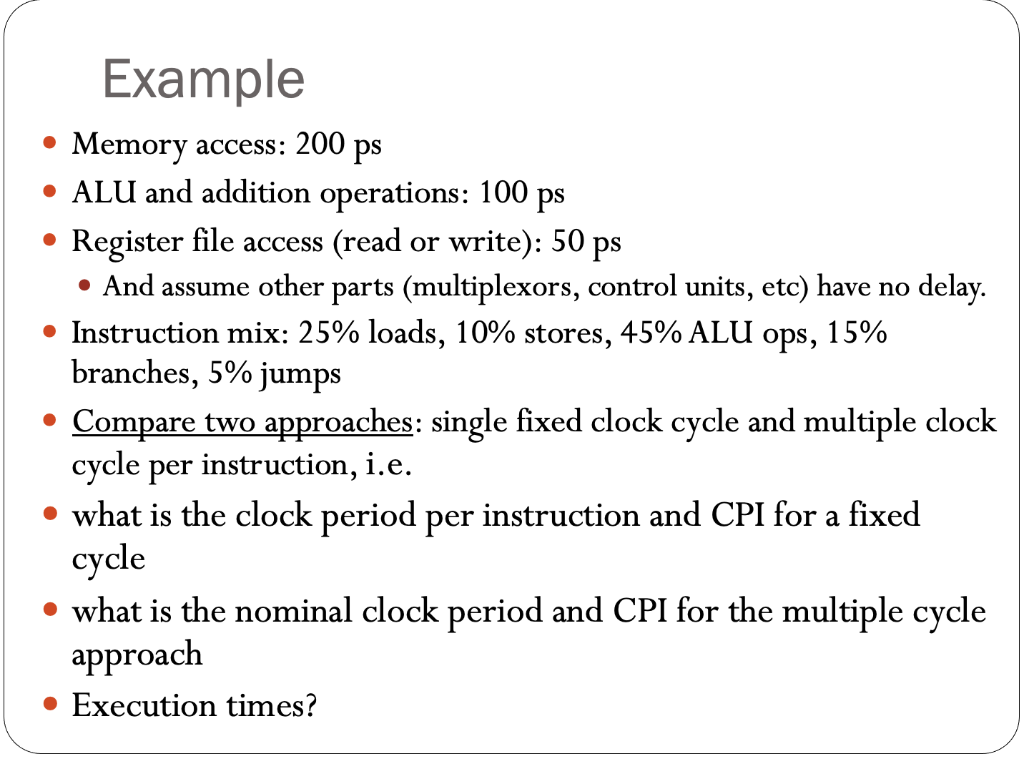

Example Memory access: 200 ps ALU and addition operations: 100 ps Register file access (read or write): 50 ps And assume other parts (multiplexors, control units, etc) have no delay. Instruction mix: 25% loads, 10% stores, 45% ALU ops, 15% branches, 5% jumps Compare two approaches: single fixed clock cycle and multiple clock cycle per instruction, i.e. what is the clock period per instruction and CPI for a fixed cycle what is the nominal clock period and CPI for the multiple cycle approach Execution times

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts