Question: Exercise 5 a ) Draw the gate level design of a 4 - bit ripple carry adder using the above full adder. b ) What

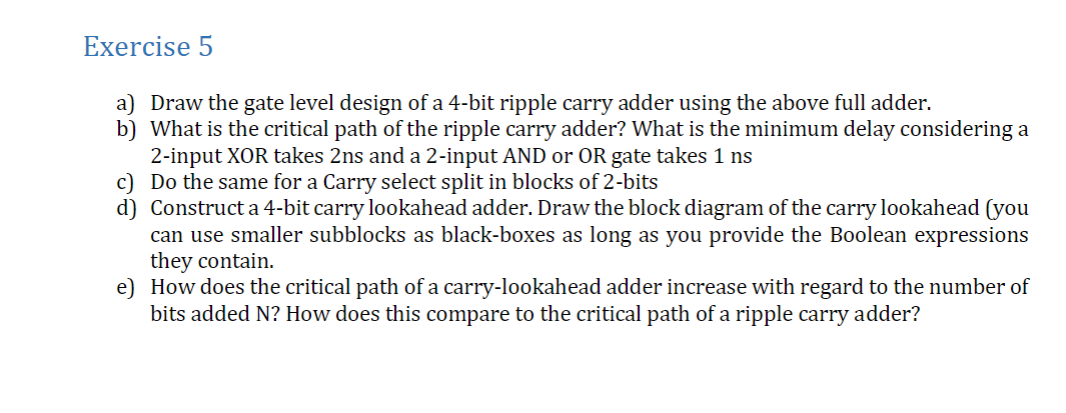

Exercise

a Draw the gate level design of a bit ripple carry adder using the above full adder.

b What is the critical path of the ripple carry adder? What is the minimum delay considering a

input XOR takes ns and a input AND or OR gate takes

c Do the same for a Carry select split in blocks of bits

d Construct a bit carry lookahead adder. Draw the block diagram of the carry lookahead you

can use smaller subblocks as blackboxes as long as you provide the Boolean expressions

they contain.

e How does the critical path of a carrylookahead adder increase with regard to the number of

bits added N How does this compare to the critical path of a ripple carry adder?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock