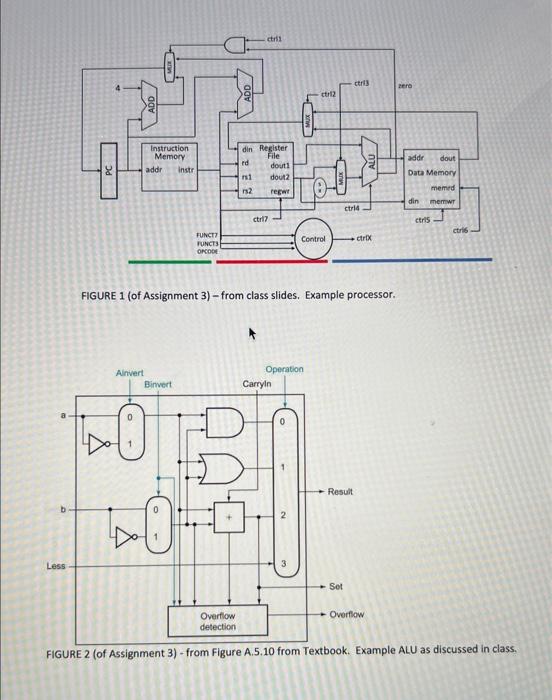

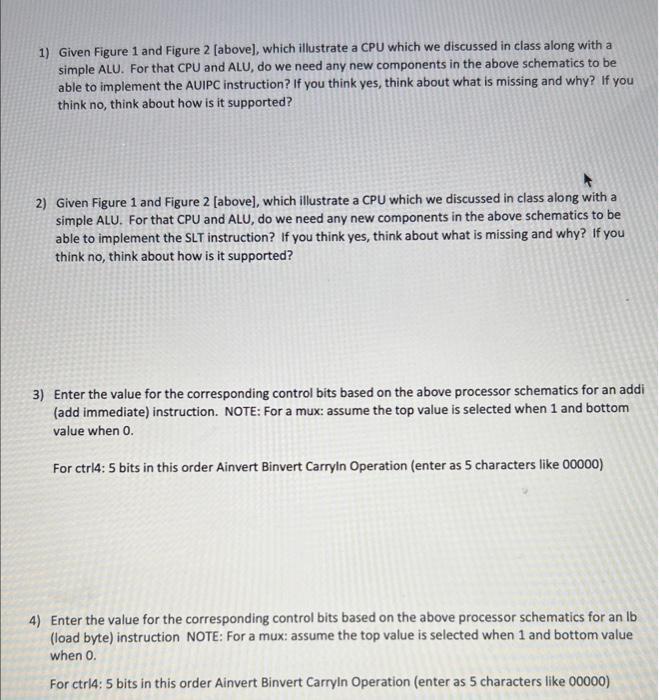

Question: FIGURE 1 (of Assignment 3 ) - from class slides. Example processor. FIGURE 2 (of Assignment 3) - from Figure A.5.10 trom Textbook. txample ALU

FIGURE 1 (of Assignment 3 ) - from class slides. Example processor. FIGURE 2 (of Assignment 3) - from Figure A.5.10 trom Textbook. txample ALU as discussed in class. 1) Given Figure 1 and Figure 2 [above], which illustrate a CPU which we discussed in class along with a simple ALU. For that CPU and ALU, do we need any new components in the above schematics to be able to implement the AUIPC instruction? If you think yes, think about what is missing and why? If you think no, think about how is it supported? 2) Given Figure 1 and Figure 2 [above], which illustrate a CPU which we discussed in class along with a simple ALU. For that CPU and ALU, do we need any new components in the above schematics to be able to implement the SLT instruction? If you think yes, think about what is missing and why? If you think no, think about how is it supported? 3) Enter the value for the corresponding control bits based on the above processor schematics for an addi (add immediate) instruction. NOTE: For a mux: assume the top value is selected when 1 and bottom value when 0 . For ctrl4: 5 bits in this order Ainvert Binvert Carryln Operation (enter as 5 characters like 00000) 4) Enter the value for the corresponding control bits based on the above processor schematics for an Ib (load byte) instruction NOTE: For a mux: assume the top value is selected when 1 and bottom value when 0. For ctrl4: 5 bits in this order Ainvert Binvert Carryln Operation (enter as 5 characters like 00000)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts