Question: First create a circuit called 1-bitAdder with three inputs a,b, carryIn, two outputs sum and carryout. Remember input is a square and output is a

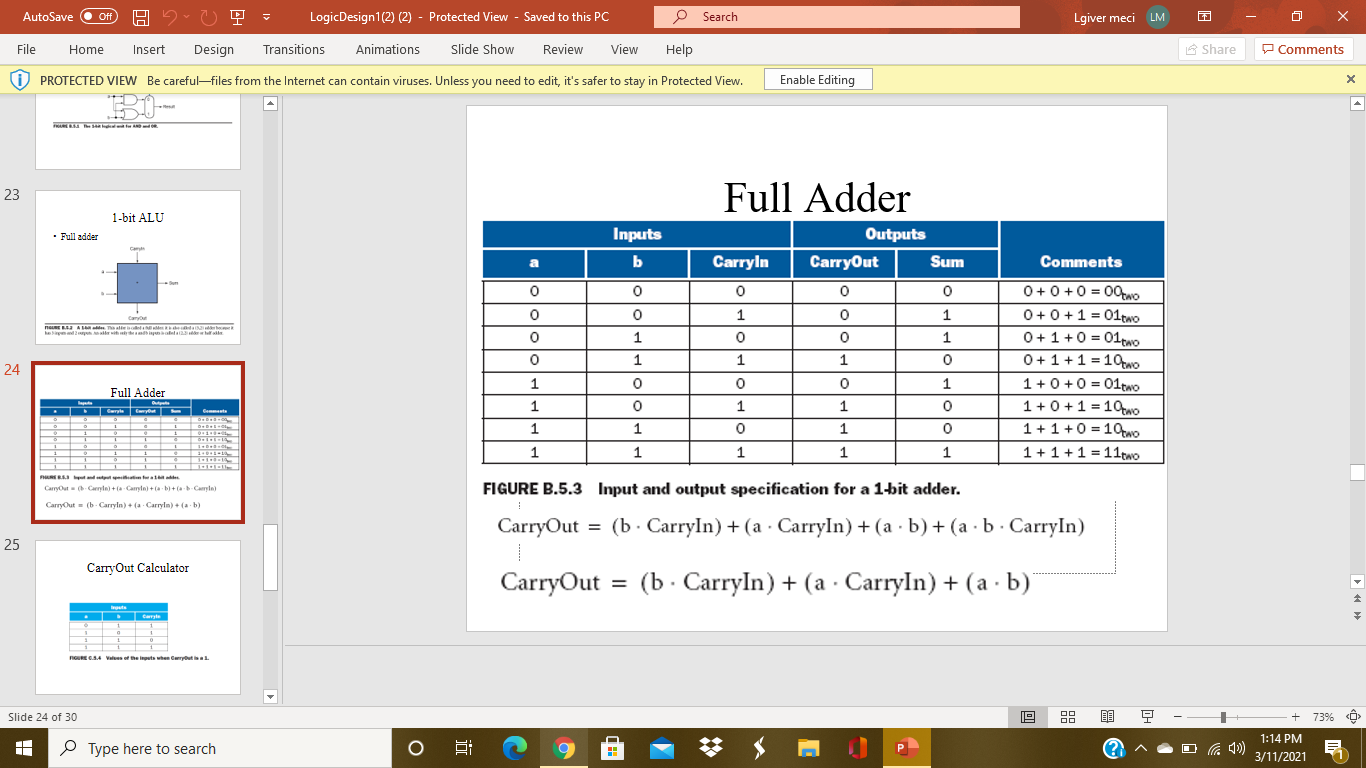

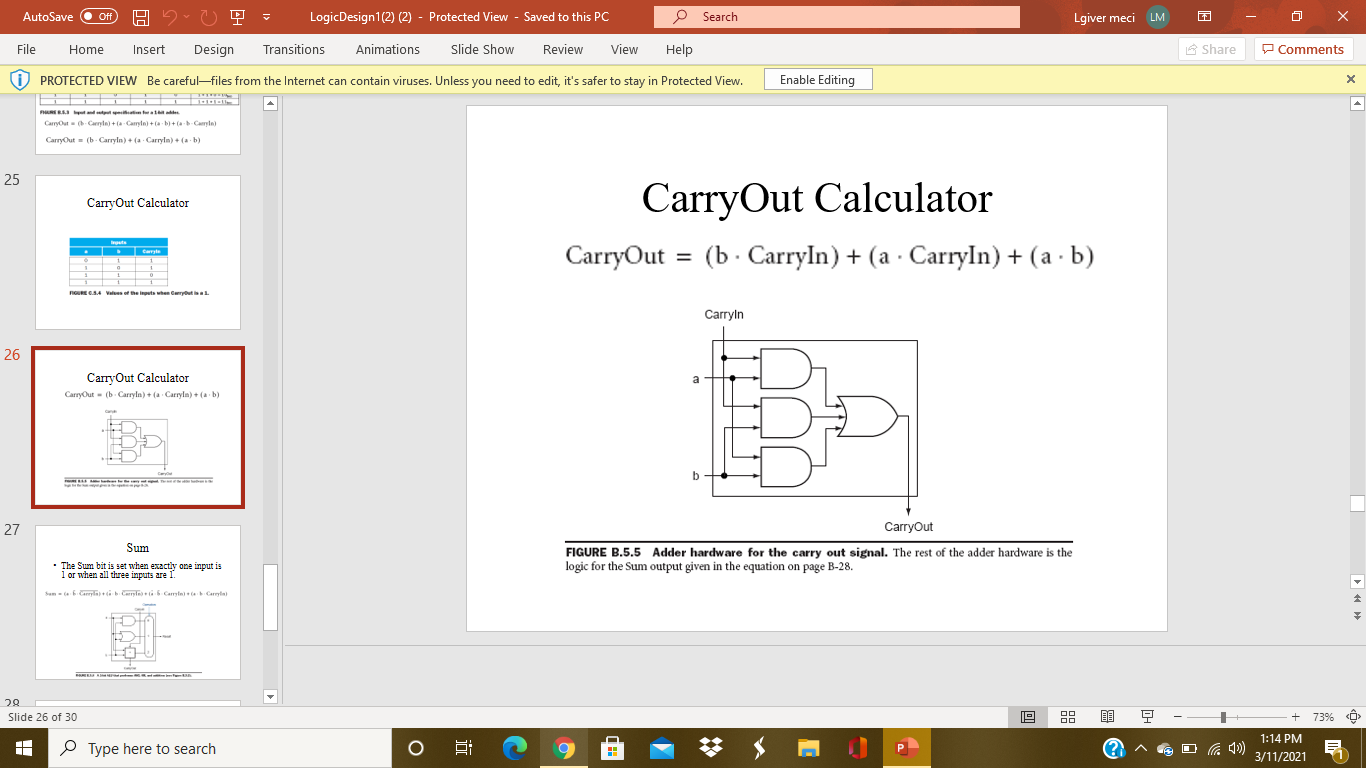

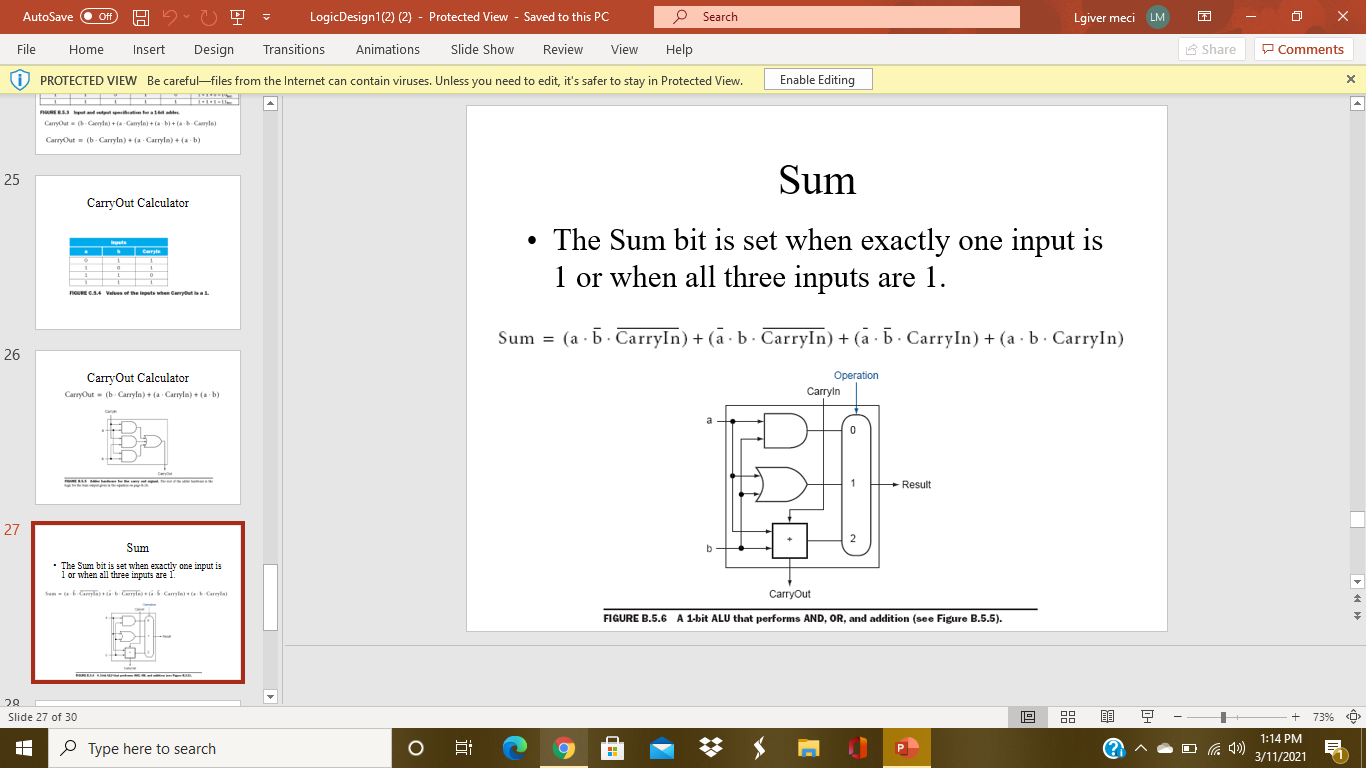

First create a circuit called 1-bitAdder with three inputs a,b, carryIn, two outputs sum and carryout. Remember input is a square and output is a circle. You may use logical equation in slide 24 or combine slide 26 and 27 in LogicalDesign1.pptx. You may also follow what I did in class.

First create a circuit called 1-bitAdder with three inputs a,b, carryIn, two outputs sum and carryout. Remember input is a square and output is a circle. You may use logical equation in slide 24 or combine slide 26 and 27 in LogicalDesign1.pptx. You may also follow what I did in class.

AutoSave Off H bu o - LogicDesign1(2) (2) - Protected View - Saved to this PC O Search Lgiver meci LM File Home Insert Design Transitions Animations Slide Show Review View Help Share Comments i PROTECTED VIEW Be carefulfiles from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable Editing X 23 Full Adder 1-bit ALU Full adder Inputs Outputs CarryOut Sum b Carryin Comments 0 o 0 0 0 0 0 0 NORBE A Ride. The aller be 1 0 . 0 1 1 0 1 1 1 0 1 0 1 24 0+ 0 + 0 = 0 0 0 0 + 0 + 1 = 01two 0 + 1 + 0 = 01 No 0 + 1 + 1 = 10NO 1 + 0 + 0 = 01two 1 + 0 + 1 = 10 No 1 + 1 + 0 = 1 NO 1 + 1 + 1 = 11two 1 0 Full Adder 1 0 0 1 0 0 1 1 0 1 0 1 1 1 1 1 1 CarryOut (Caye) + la-Carryin)+(ab)+(Caryle) CarryOut = (b-Carryin) + (a Carryin)+(ab) FIGURE B.5.3 Input and output specification for a 1-bit adder. CarryOut = (b Carryin) + (a CarryIn) +(a - b)+(a b. CarryIn) 25 CarryOut Calculator CarryOut = = (b CarryIn) + (a CarryIn) + (a.b) Caryle 1 Slide 24 of 30 12 + 73% Type here to search > ? 1:14 PM 3/11/2021 AutoSave Off H bu o LogicDesign1(2) (2) - Protected View - Saved to this PC O Search Lgiver meci LM File Home Insert Design Transitions Animations Slide Show Review View Help Share Comments i PROTECTED VIEW Be carefulfiles from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable Editing X CarryOw-Cara-Carryin tabiiy CarryOut (bCarryin)+(a Carryla) (b) 25 CarryOut Calculator CarryOut Calculator CarryOut (b Carryin) + (a Carryin) + (a.b) Inputs Carryle = + FIGURE 6.3.4 Vals of the inputs when you Carryin 26 a CarryOut Calculator CarryOut - (b. Carryin) + (a Carryla) +(ab) b 27 CarryOut Sum The Sum bit is set when exactly one input is 1 or when all three inputs are 1. FIGURE B.5.5 Adder hardware for the carry out signal. The rest of the adder hardware is the logic for the Sum output given in the equation on page B-28. 29 Slide 26 of 30 12 + 73% 1:14 PM Type here to search > . ? 3/11/2021 AutoSave HI LogicDesign 1(2) (2) - Protected View - Saved to this PC Search Lgiver meci LM File Home Insert Design Transitions Animations Slide Show Review View Help Share Comments i PROTECTED VIEW Be carefulfiles from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable Editing X CarryOw-Cara-Carryin tabiiy CarryOut (bCarryin)+(a Carryla) (b) 25 Sum CarryOut Calculator The Sum bit is set when exactly one input is 1 or when all three inputs are 1. NG 14 white when you sal Sum = (a - 5. CarryIn) +(.b. CarryIn) +(5:5. CarryIn) +(a. b. Carryin) 26 CarryOut Calculator CarryOut (b. Carryin) + (a Carryin) +(ab) Operation Carryin BE Result 27 2 Sum The Sum bit is set when exactly one input is 1 or when all three inputs are 1. CarryOut FIGURE B.5.6 A 1-bit ALU that performs AND, OR, and addition (see Figure B.5.5). 20 Slide 27 of 30 12 73% I Type here to search > . 1:14 PM 3/11/2021 AutoSave Off H bu o - LogicDesign1(2) (2) - Protected View - Saved to this PC O Search Lgiver meci LM File Home Insert Design Transitions Animations Slide Show Review View Help Share Comments i PROTECTED VIEW Be carefulfiles from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable Editing X 23 Full Adder 1-bit ALU Full adder Inputs Outputs CarryOut Sum b Carryin Comments 0 o 0 0 0 0 0 0 NORBE A Ride. The aller be 1 0 . 0 1 1 0 1 1 1 0 1 0 1 24 0+ 0 + 0 = 0 0 0 0 + 0 + 1 = 01two 0 + 1 + 0 = 01 No 0 + 1 + 1 = 10NO 1 + 0 + 0 = 01two 1 + 0 + 1 = 10 No 1 + 1 + 0 = 1 NO 1 + 1 + 1 = 11two 1 0 Full Adder 1 0 0 1 0 0 1 1 0 1 0 1 1 1 1 1 1 CarryOut (Caye) + la-Carryin)+(ab)+(Caryle) CarryOut = (b-Carryin) + (a Carryin)+(ab) FIGURE B.5.3 Input and output specification for a 1-bit adder. CarryOut = (b Carryin) + (a CarryIn) +(a - b)+(a b. CarryIn) 25 CarryOut Calculator CarryOut = = (b CarryIn) + (a CarryIn) + (a.b) Caryle 1 Slide 24 of 30 12 + 73% Type here to search > ? 1:14 PM 3/11/2021 AutoSave Off H bu o LogicDesign1(2) (2) - Protected View - Saved to this PC O Search Lgiver meci LM File Home Insert Design Transitions Animations Slide Show Review View Help Share Comments i PROTECTED VIEW Be carefulfiles from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable Editing X CarryOw-Cara-Carryin tabiiy CarryOut (bCarryin)+(a Carryla) (b) 25 CarryOut Calculator CarryOut Calculator CarryOut (b Carryin) + (a Carryin) + (a.b) Inputs Carryle = + FIGURE 6.3.4 Vals of the inputs when you Carryin 26 a CarryOut Calculator CarryOut - (b. Carryin) + (a Carryla) +(ab) b 27 CarryOut Sum The Sum bit is set when exactly one input is 1 or when all three inputs are 1. FIGURE B.5.5 Adder hardware for the carry out signal. The rest of the adder hardware is the logic for the Sum output given in the equation on page B-28. 29 Slide 26 of 30 12 + 73% 1:14 PM Type here to search > . ? 3/11/2021 AutoSave HI LogicDesign 1(2) (2) - Protected View - Saved to this PC Search Lgiver meci LM File Home Insert Design Transitions Animations Slide Show Review View Help Share Comments i PROTECTED VIEW Be carefulfiles from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable Editing X CarryOw-Cara-Carryin tabiiy CarryOut (bCarryin)+(a Carryla) (b) 25 Sum CarryOut Calculator The Sum bit is set when exactly one input is 1 or when all three inputs are 1. NG 14 white when you sal Sum = (a - 5. CarryIn) +(.b. CarryIn) +(5:5. CarryIn) +(a. b. Carryin) 26 CarryOut Calculator CarryOut (b. Carryin) + (a Carryin) +(ab) Operation Carryin BE Result 27 2 Sum The Sum bit is set when exactly one input is 1 or when all three inputs are 1. CarryOut FIGURE B.5.6 A 1-bit ALU that performs AND, OR, and addition (see Figure B.5.5). 20 Slide 27 of 30 12 73% I Type here to search > . 1:14 PM 3/11/2021

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts