Question: For a direct mapped cache design with a 64-bit address, the following bits of the address are used to access the cache 5.5.1 what is

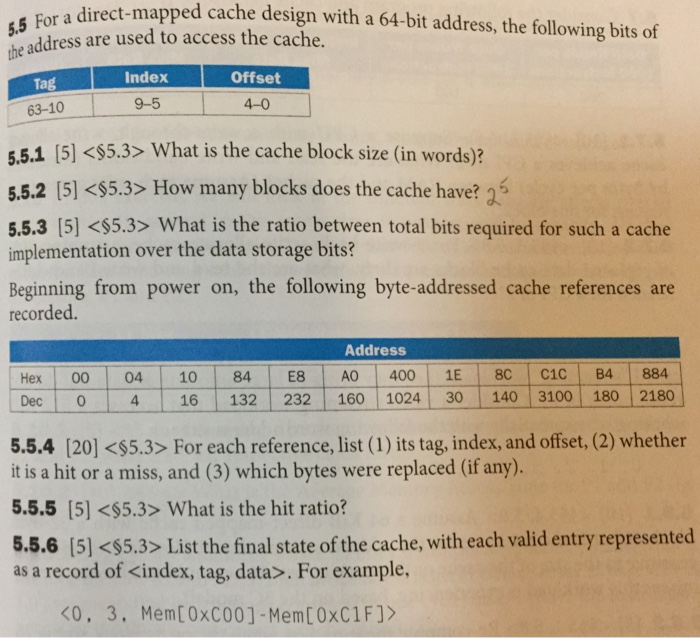

direct-mapped cache design with a 64-bit address, the following bits of For a address are used to access the cache. Index Offset Tag 9-5 4-0 63-10 5.5.1 [5] What is the cache block size (in words)? 5.5.2 [5] How many blocks does the cache have? 25 5.5.3 [5] What is the ratio between total bits required for such a cache implementation over the data storage bits? Beginning from power on, the following byte-addressed cache references are recorded. Address Hex 00 04 10 84 E8AO 400 1E8C C1C B4 884 Dec 0 4 16 132 232 160 1024 30 140 3100 180 2180 5.5.4 [20] For each reference, list (1) its tag, index, and offset, (2) whether it is a hit or a miss, and (3) which bytes were replaced (if any). 5.5.5 [5] What is the hit ratio? 5.5.6 (5) List the final state of the cache, with each valid entry represented as a record of

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts