Question: For problems 7 through 9, consider a CPU that implements two parallel fetch-execute pipelines for superscalar processing. Show the performance improvement over scalar pipeline processing

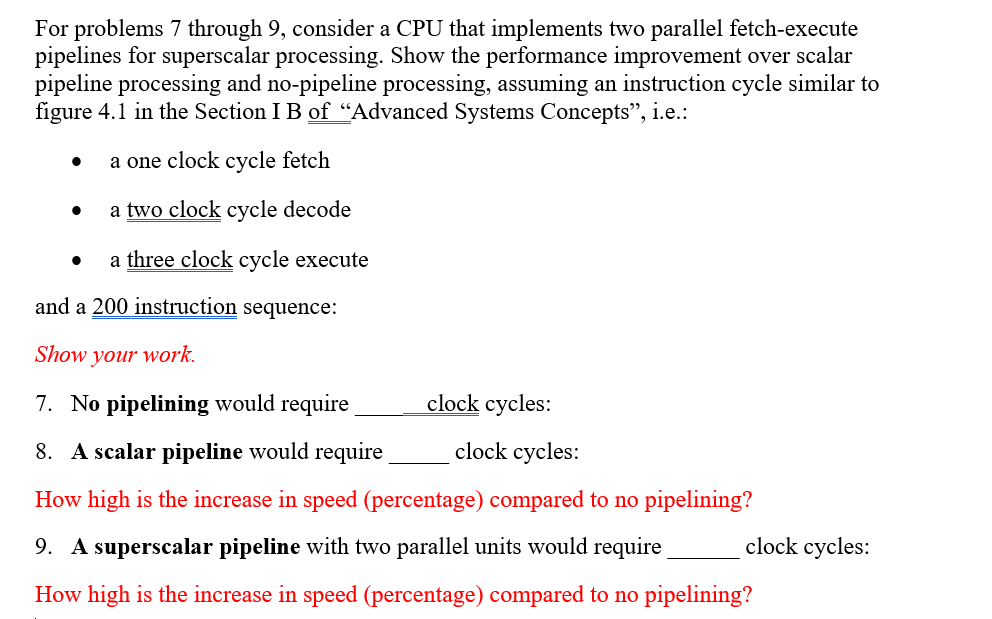

For problems 7 through 9, consider a CPU that implements two parallel fetch-execute pipelines for superscalar processing. Show the performance improvement over scalar pipeline processing and no-pipeline processing, assuming an instruction cycle similar to figure 4.1 in the Section I B of Advanced Systems Concepts, i.e.: a one clock cycle fetch . a two clock cycle decode . a three clock cycle execute and a 200 instruction sequence: Show your work. 7. No pipelining would require clock cycles: 8. A scalar pipeline would require clock cycles: How high is the increase in speed (percentage) compared to no pipelining? 9. A superscalar pipeline with two parallel units would require clock cycles: How high is the increase in speed (percentage) compared to no pipelining

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts