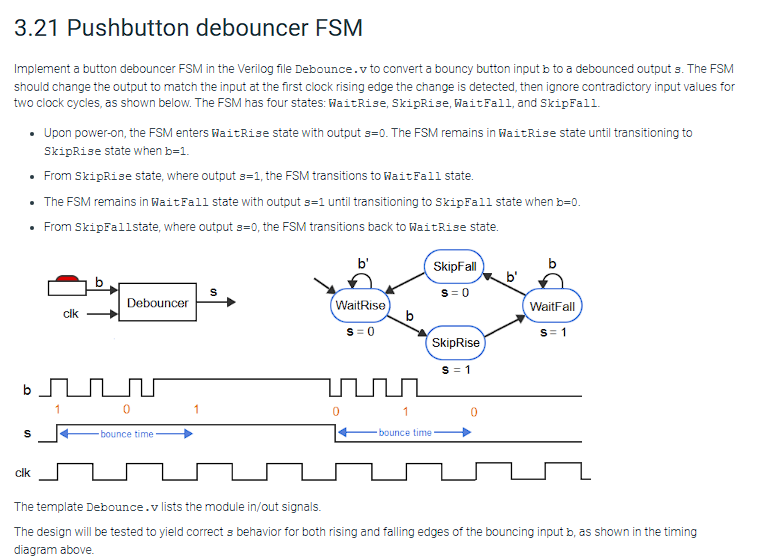

Question: FSM Debouncer implementation on verilog. I get errors at 3 5 ns and 1 0 5 ns . Testbench is correct. Code I have tried:

FSM Debouncer implementation on verilog. I get errors at ns and ns Testbench is correct. Code I have tried:

module Debounce

input clk b b is the bouncy pushbutton or switch

output reg s debounced version of pushbutton, synchronized to clock

;

State encoding

localparam :

WaitRise b

SkipRise b

WaitFall b

SkipFall b;

reg : currentstate, nextstate;

Synchronous state transition

always @posedge clk begin

currentstate nextstate;

end

Nextstate logic and output logic

always @ begin

Default values

nextstate currentstate;

s ; Default output is

case currentstate

WaitRise: begin

s ; Output is in WaitRise

if b nextstate SkipRise; Transition to SkipRise on b

end

SkipRise: begin

s ; Output is in SkipRise

nextstate WaitFall; Transition to WaitFall after one clock

end

WaitFall: begin

s ; Output remains in WaitFall

if b nextstate SkipFall; Transition to SkipFall on b

end

SkipFall: begin

s ; Output is in SkipFall

nextstate WaitRise; Transition to WaitRise after one clock

end

default: begin

nextstate WaitRise; Default state fallback

end

endcase

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock