Question: Given the following single cycle MIPS processor architecture. Instruction (25-01 Shift left 2 Jump address (31-01 28 PC 4[31-2811 26 Add Add Shift left 2)

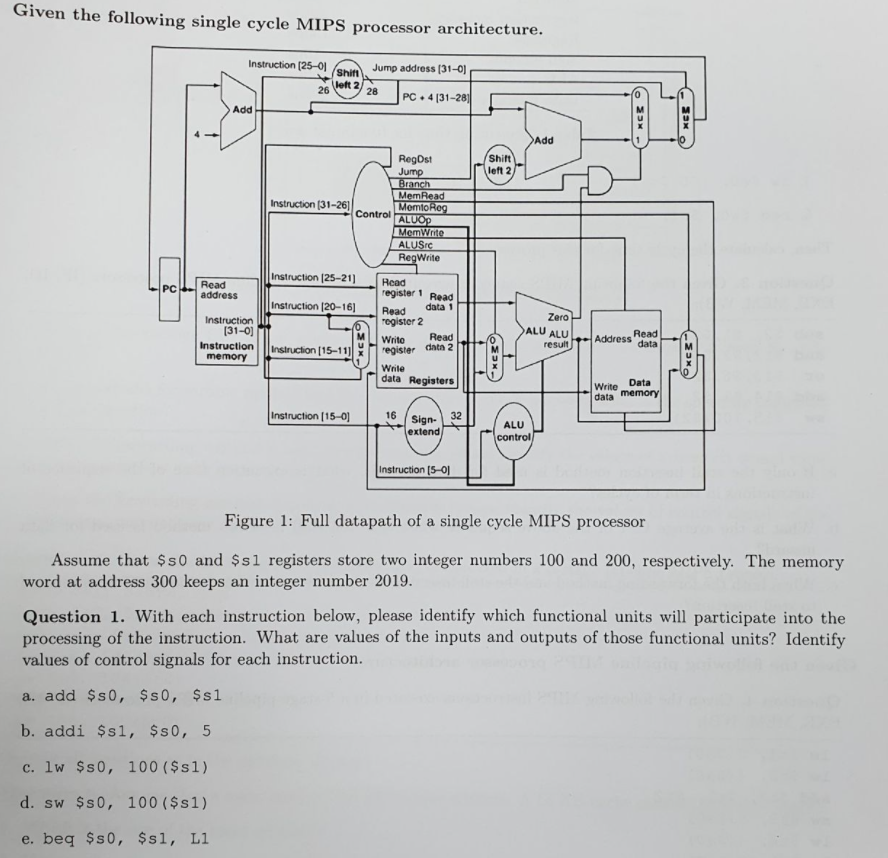

Given the following single cycle MIPS processor architecture. Instruction (25-01 Shift left 2 Jump address (31-01 28 PC 4[31-2811 26 Add Add Shift left 2) RegDst Jump Branch MemRead Instruction (31-26] Momto Rog Control ALUOP MemWrite ALUS RegWrite Instruction (25-21) Read register1 Read Instruction (20-16) data 1 Read register 2 Writo Read Instruction (15-11) Write data Registers PC Read address Zero ALU ALU Instruction (31-0) Instruction memory Read Address result data register data 2 *KETO Write Data data memory Instruction 15-01 16 32 Sign- extend ALU control Instruction 15-01 Figure 1: Full datapath of a single cycle MIPS processor Assume that $50 and $s1 registers store two integer numbers 100 and 200, respectively. The memory word at address 300 keeps an integer number 2019. Question 1. With each instruction below, please identify which functional units will participate into the processing of the instruction. What are values of the inputs and outputs of those functional units? Identify values of control signals for each instruction. a. add $s0, $s0, $s1 b. addi $81, $50, 5 c. lw $50, 100 ($s1) d. sw $50, 100 ($51) e. beg $50, $81, Li

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts