Question: In a symmetric multiprocessor (SMP) system with a shared bus, there are three CPUs (CPU1, CPU2, and CPU3) that have local cache memories. The

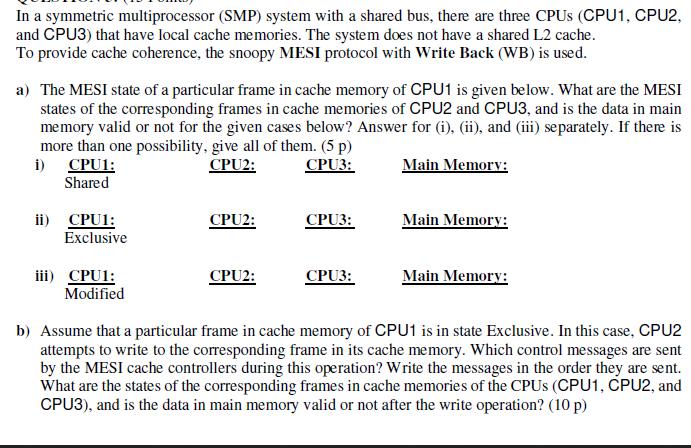

In a symmetric multiprocessor (SMP) system with a shared bus, there are three CPUs (CPU1, CPU2, and CPU3) that have local cache memories. The system does not have a shared L2 cache. To provide cache coherence, the snoopy MESI protocol with Write Back (WB) is used. a) The MESI state of a particular frame in cache memory of CPU1 is given below. What are the MESI states of the corresponding frames in cache memories of CPU2 and CPU3, and is the data in main memory valid or not for the given cases below? Answer for (i), (ii), and (iii) separately. If there is more than one possibility, give all of them. (5 p) i) CPU1: CPU2: CPU3: Main Memory: Shared ii) CPU1: CPU2: CPU3: Main Memory: Exclusive iii) CPU1: Modified CPU2: CPU3: Main Memory: b) Assume that a particular frame in cache memory of CPU1 is in state Exclusive. In this case, CPU2 attempts to write to the corresponding frame in its cache memory. Which control messages are sent by the MESI cache controllers during this operation? Write the messages in the order they are sent. What are the states of the corresponding frames in cache memories of the CPUS (CPU1, CPU2, and CPU3), and is the data in main memory valid or not after the write operation? (10 p)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts