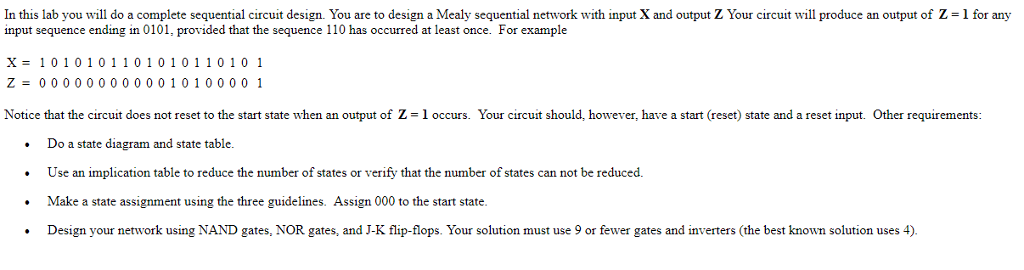

Question: In this lab you will do a complete sequential circuit design. You are to design a Mealy sequential network with input X and output Z

In this lab you will do a complete sequential circuit design. You are to design a Mealy sequential network with input X and output Z Your circuit will produce an output of Z-1 for any input sequence ending in 0101, provided that the sequence 110 has occurred at least once. For example X= 101010110101011010 1 Z 0 00000 0 00 0010 1 0000 1 Notice that the circuit does not reset to the start state when an output of Z1 occurs. Your circuit should, however, have a start (reset) state and a reset input. Other requirements: Do a state diagram and state table. Use an implication table to reduce the number of states or verify that the number of states can not be reduced. Make a state assignment using the three guidelines. Assign 000 to the start state Design your network using NAND gates, NOR gates, and J-K flip-flops. Your solution must use 9 or fewer gates and inverters (the best known solution uses 4) In this lab you will do a complete sequential circuit design. You are to design a Mealy sequential network with input X and output Z Your circuit will produce an output of Z-1 for any input sequence ending in 0101, provided that the sequence 110 has occurred at least once. For example X= 101010110101011010 1 Z 0 00000 0 00 0010 1 0000 1 Notice that the circuit does not reset to the start state when an output of Z1 occurs. Your circuit should, however, have a start (reset) state and a reset input. Other requirements: Do a state diagram and state table. Use an implication table to reduce the number of states or verify that the number of states can not be reduced. Make a state assignment using the three guidelines. Assign 000 to the start state Design your network using NAND gates, NOR gates, and J-K flip-flops. Your solution must use 9 or fewer gates and inverters (the best known solution uses 4)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts