Question: In this question, we examine how resource hazards, control hazards, and ISA design can affect pipelined execution. Problems in this exercise refer to the following

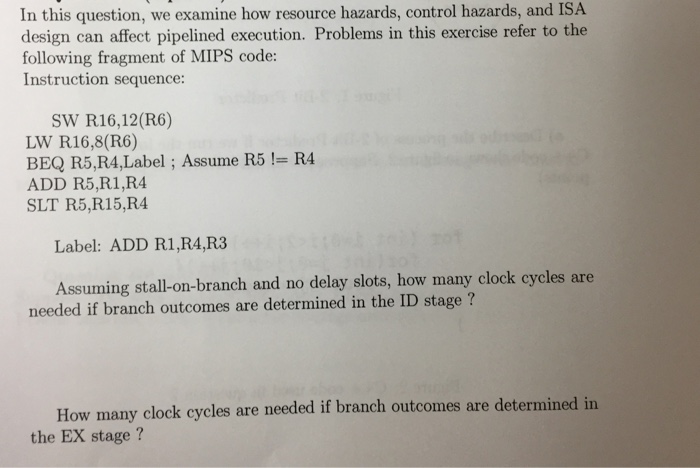

In this question, we examine how resource hazards, control hazards, and ISA design can affect pipelined execution. Problems in this exercise refer to the following fragment of MIPS code: Instruction sequence: SW R16, 12(R6) LW R16, 8(R6) BEQ R5, R4, Label; Assume R5 != R4 ADD R5, R1, R4 SLT R5, R15, R4 Label: ADD R1, R4, R3 Assuming stall-on-branch and no delay slots, how many clock cycles are needed if branch outcomes are determined in the ID stage ? How many clock cycles are needed if branch outcomes are determined in the EX stage

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts