Question: Instruction producing result Instruction using resultLatency in clock cycles FP ALU o FP ALU o FP ALU o Load double Load double Another FP ALUo

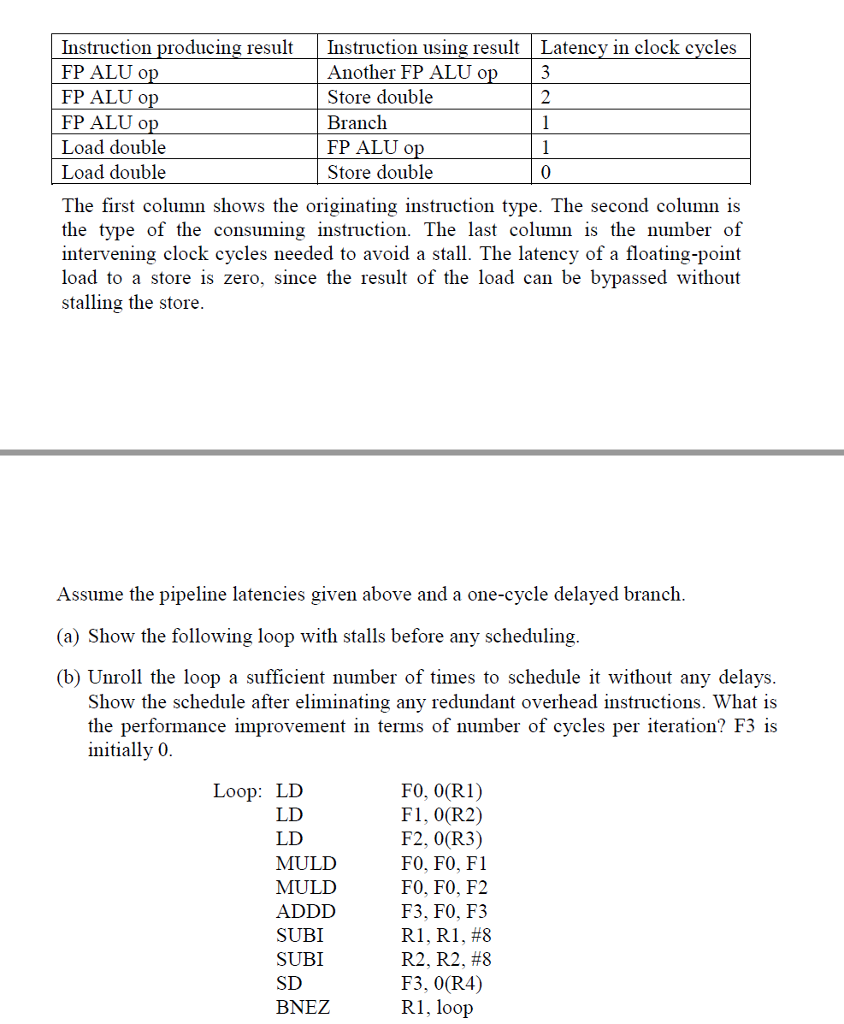

Instruction producing result Instruction using resultLatency in clock cycles FP ALU o FP ALU o FP ALU o Load double Load double Another FP ALUo Store double Branch FP ALU o Store double 0 The first column shows the originating instruction type. The second column is the type of the consuming instruction. The last column is the number of intervening clock cycles needed to avoid a stall. The latency of a floating-point load to a store is zero, since the result of the load can be bypassed without stalling the store Assume the pipeline latencies given above and a one-cycle delayed branch (a) Show the following loop with stalls before any scheduling (b) Unroll the loop a sufficient number of times to schedule it without any delays Show the schedule after eliminating any redundant overhead instructions. What is the performance improvement in terms of number of cycles per iteration? F3 is initially 0 Loop: LD LD LD MULD MULD ADDD SUBI SUBI SD BNEZ F0, 0(RI) F1, 0(R2) F2, 0(R3) FO, FO, FI F0, F0, F:2 F3. F0, F:3 RI, RI, #8 R2, R2, #8 F3, 0(R4) R1, loop Instruction producing result Instruction using resultLatency in clock cycles FP ALU o FP ALU o FP ALU o Load double Load double Another FP ALUo Store double Branch FP ALU o Store double 0 The first column shows the originating instruction type. The second column is the type of the consuming instruction. The last column is the number of intervening clock cycles needed to avoid a stall. The latency of a floating-point load to a store is zero, since the result of the load can be bypassed without stalling the store Assume the pipeline latencies given above and a one-cycle delayed branch (a) Show the following loop with stalls before any scheduling (b) Unroll the loop a sufficient number of times to schedule it without any delays Show the schedule after eliminating any redundant overhead instructions. What is the performance improvement in terms of number of cycles per iteration? F3 is initially 0 Loop: LD LD LD MULD MULD ADDD SUBI SUBI SD BNEZ F0, 0(RI) F1, 0(R2) F2, 0(R3) FO, FO, FI F0, F0, F:2 F3. F0, F:3 RI, RI, #8 R2, R2, #8 F3, 0(R4) R1, loop

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts