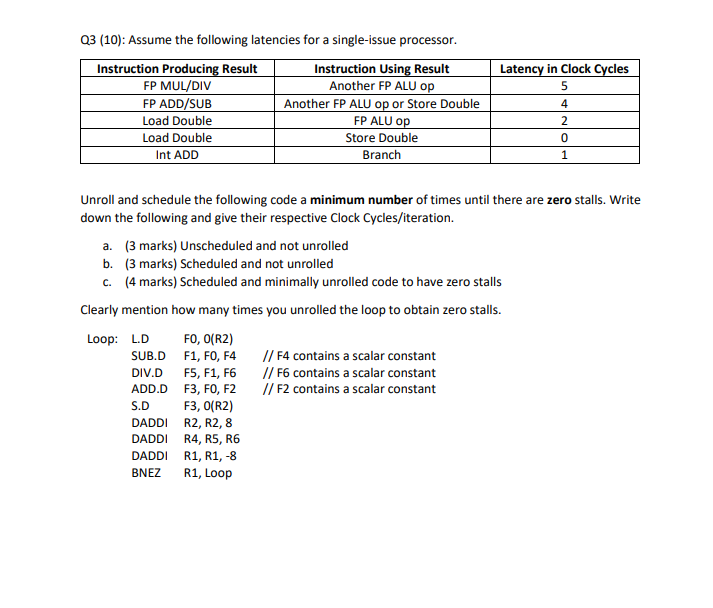

Question: Q3 (10): Assume the following latencies for a single-issue processor. Instruction Producing Result Instruction Using Result FP MUL/DIV Another FP ALU op FP ADD/SUB Another

Q3 (10): Assume the following latencies for a single-issue processor. Instruction Producing Result Instruction Using Result FP MUL/DIV Another FP ALU op FP ADD/SUB Another FP ALU op or Store Double Load Double FP ALU Op Load Double Store Double Int ADD Branch Latency in Clock Cycles 5 4 2 0 1 Unroll and schedule the following code a minimum number of times until there are zero stalls. Write down the following and give their respective Clock Cycles/iteration. a. (3 marks) Unscheduled and not unrolled b. (3 marks) Scheduled and not unrolled C. (4 marks) Scheduled and minimally unrolled code to have zero stalls Clearly mention how many times you unrolled the loop to obtain zero stalls. Loop: LD FO, O(R2) SUB.D F1, FO, F4 // F4 contains a scalar constant DIV.D F5, F1, F6 // F6 contains a scalar constant ADD.D F3, FO, F2 // F2 contains a scalar constant F3, 0(R2) DADDI R2, R2,8 DADDI R4, RS, R6 DADDI R1, R1, -8 BNEZ R1, Loop S.D

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts