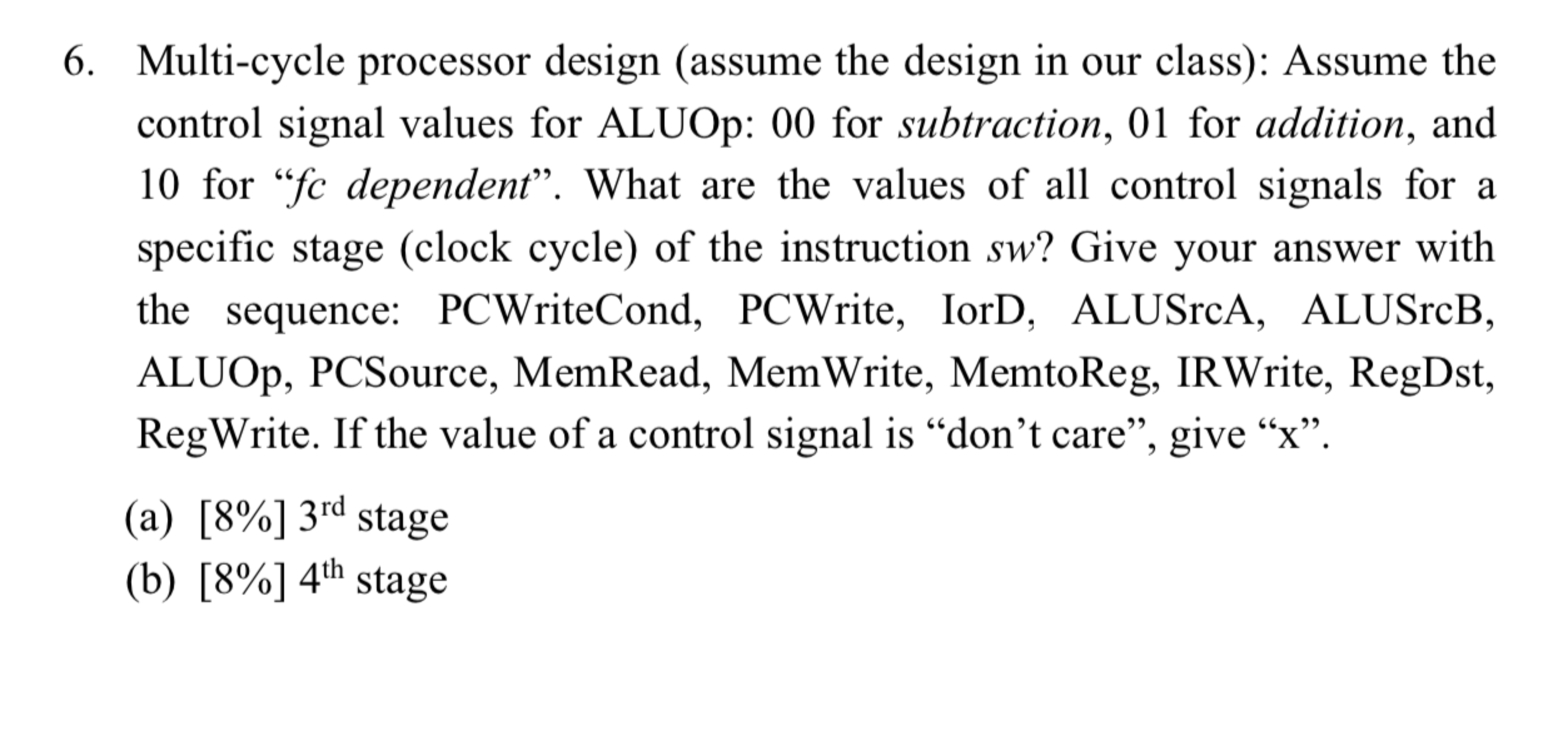

Question: Multi - cycle processor design ( assume the design in our class ) : Assume the control signal values for ALUOp: 0 0 for subtraction,

Multicycle processor design assume the design in our class: Assume the

control signal values for ALUOp: for subtraction, for addition, and

for fc dependent". What are the values of all control signals for a

specific stage clock cycle of the instruction Give your answer with

the sequence: PCWriteCond, PCWrite, IorD, ALUSrcA, ALUSrcB,

ALUOp, PCSource, MemRead, MemWrite, MemtoReg, IRWrite, RegDst,

RegWrite. If the value of a control signal is "don't care", give

a stage

b stage

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock